**Cover**Story

Chairman Chief Scientist

Synergy Microwave Corp., 202 McLean Blvd., Paterson, NJ 07504; +1-973-881-8800; FAX: +1-973-881-8361, e-mail: sales@synergymwave.com, www.synergymwave.com

## Synthesizers Shave Size And Noise

THESE SYNTHESIZERS ENLIST

DDS TECHNOLOGY IN

COMBINATION WITH A VCO

TO ACHIEVE LOW PHASE

NOISE AND EXCELLENT

SPURIOUS PERFORMANCE—

DOING SO AT A FRACTION

OF THE SIZE AND COST

OF CONVENTIONAL PLL

SYNTHESIZERS.

REQUENCY SYNTHESIZERS are the essential signal sources for many high-frequency systems, from communications to test platforms. Synthesizers come in many forms, ranging from tiny system-on-achip (SoC) devices to large rack-mount units 1-41 The number of technologies used to implement them is almost as diverse as their package styles, relying on analog methods, digital techniques, and sometimes a combination of the two approaches. For many applications, basic frequency synthesizer requirements call for a small unit with excellent spectral purity, but at an affordable price. These simple requirements drove the development of a new line of low-noise sources based on direct-digital synthesis (DDS) from Synergy Microwave Corp. (www. synergymwave.com)-one that comes at a fraction of the size and cost of currently available commercial sources.

Regardless of package style and size, frequency synthesizers can be differentiat-

ed by a number of key performance specifications. These include frequency tuning range (if not a fixed-frequency synthesizer), output power, output-power flatness across the tuning range, and a number of other parameters! Acceptable levels for these parameters are usually set by the application of interest. Something like fast switching speed, for example, would be important in a frequency-agile communications system, but not as much as in other types of communications systems.<sup>2</sup>

One of the more common types of synthesizer is a voltage-controlled oscillator. (VCO) stabilized by a phase-locked loop (PLL). A conventional PLL-based frequency synthesizer includes a reference phase detector, loop filter, VCO, and VCO divider (Fig. 1).<sup>3</sup> Equation 1 defines the relationship between the output frequency, f<sub>coli</sub>, and reference frequency, f<sub>col</sub>.

$f_{out} = N x (f_{ref}/R)$  (1)

The phase-frequency detector (FFD) compares the two input signals  $\zeta_{\rm mf} R$  and  $f_{\rm out} N$  and produces an error voltage proportional to the phase difference between them. The loop filter removes the high-frequency noise components from the FD's output and limits the bandwidth of the error signal. The filtered error voltage is applied to the tuning port of the VCO to stabilize its resulting tuned frequency; the error signal drives the VCO frequency ( $\zeta_{\rm inp}$ ) so that the error voltage at the PED output

This block diagram shows a simplified

PLL synthesizer module.

132 May 2012 | Microwaves&RF

This phase-noise plot typifies the performance of an integer-N PLL synthesizer.

is zero when locked.5

Typically, the VCO divider is implemented as a dual-modulus counter to botain large continuous division of the VCO output. To vary synthesizer output frequency, f<sub>out</sub>. N is changed. As Eq. 1 shows, the minimum output frequency step is f<sub>out</sub>/R. Operating the PFD at a lower frequency makes it possible to achieve a smaller step, but also increases R and N; in increasing N, the PFD noise also increases. A PLL synthesizer's close-in phase noise is estimated by adding the noise of the synthesizer, PN<sub>SNR</sub> to 20logN (where N is the divider value) and 10log/<sub>FDD</sub>:

$$\begin{split} &PN_{TOT} = PN_{SYN} + 10logf_{PFD} + 20logN \\ &= PN_{SYN} + 10log(f_{REF}/R) + 20logN \end{split} \tag{2}$$

$PN_{PD}$  (dBc/Hz) =  $PLL_{FOM}$  +  $20log_{10}(f_{VCO}$  -  $10log(f_{PD})$  (frequencies are in Hz) (3)

These simple equations reweal that PLL synthesizer design is a matter of tradeoffs.<sup>2-4</sup> As Eq. 2 shows, N should be low to minimize phase noise. But fine frequency resolution results from a PED that is low in frequency, which leads to an increase in N and degraded noise performance. While loop filters can limit noise, they also prevent fast switching speed. A higher loop filter bandwidth yields faster switching speed, yet allows noise to pass. A narrower loop filter cuts the noise level, but with slower switching speed.

PLL frequency synthesizers can be implemented with integer or fractional values of N. Figure 2 shows the typical phase noise characteristics of an integer. M frequency synthesizer (model FSW50120-50; see ref. 27) that tunes from 500 to 1200 MHz with 500-kHz step size and under

5-ms switching speed. The typical spurious noise is -65 dBc when operating with a 10-MHz reference frequency. To improve the performance of the integer-N frequency synthesizer, divider N can be implemented as a fractional divider rather than an integer divider.

For example (as shown in Fig. 3), a commercial fractional-N source (model LFSW160290-50; see ref. 27), that tunes from 1600 to 2900 MHz in 500-kHz steps and works with a 10-MHz reference might have spurious levels of -60 dBc and switching speed of 1 ms. When better frequency resolution is needed, a DDS-based multiloop synthesizer design can be used, such as in Fig. 4. In this case, the DDS clock is fed by a selectable frequency synthesizer which provides a fixed set of frequencies based on the parallel selection lines. The DDS unit, with its resolution measured in microhertz, provides the fine frequency resolution. As with other frequency synthesizer designs, a DDS suffers tradeoffs, notably poor spectral purity and high spurious levels.

DDS spurious signal components that all within the loop bandwidth are not attenuated by the loop filter. But they can be predicted and moved in frequency by using a different DDS clock frequency. With this approach, the PFD frequency of the output synthesizer can be high, improving phase-noise performance with a 10-MHz reference while still achieving 1-14z frequency resolution. Such a design has switching speed of better than 1 ms with low phase noise and better than 1-70 spurious performance from 1.1 to 2.5 GHz.

Figure 5 shows a typical block diagram for a DDS-based low-noise, fast-switching synthesizer based on a VCSO source. The typical synthesizer generates output aranging from 530 to 630 MHz with 1-MHz step size and spurious of -70 dBc or better. Since the analog phase detector has a low noise floor, the synthesizer bandwidth was kept large for faster switching time (about 200 µs) with low phase-noise performance. With recent developments in frequency synthesizers, the DDS shown in Fig. 5 can be replaced with a single-chip fliving-adder-based synthesizer.

3. This phase-noise plot shows the typical performance of an fractional-N PLL synthesizer.

This block diagram shows a typical DDS-based dual-loop frequency synthesizer.

A design team at Synergy Microwave Corp., led by Dr. Dorin Calbaza, took on the challenge of developing a synthesizer that provided high performance in a compact size (3.25 x 2.25 x 1.25 in.) and could sell for low cost. The first consideration was to use an oscillator with octave tuning range of 4 to 8 GHz, as described in ref. 2. Octave tuning allows division by two, and frequencies above 4 GHz could be successively generated. Unfortunately, process. voltage, and temperature variations would make it difficult to guarantee frequency with precision any better than a few MHz. And synchronization techniques, such as locking the oscillator to a stable reference source such as an oven-controlled crystal oscillator (OCXO), would be needed for stabilization, As Fig. 1 shows, a single-loop PLL can stabilize any frequency to the maximum oscillator's frequency.

In this approach, the low-noise crystal oscillator's frequency is multiplied by the PLL to the desired output frequency. Because of frequency multiplication, a 20 dB/decade degradation in phase noise is expected. For a 10-MHz crys-

tal oscillator with phase noise of -174 dBc/Hz offset 10 kHz, the phase noise with multiplication at 8 GHz could not be better than -115 dBc/Hz. Taking advantage of PLL behavior, the PLL loop bandwidth would ideally be set to the frequency where the -115 dBc/Hz multiplied noise floor of the crystal intersects the trace of the noise produced by the oscillator—about 400 kHz for a typical scheme.

This is rather idealized, since the phase detector and the frequency dividers used in this PLL can degrade the crystal noise floor by about 20 to 30 dB in commercial PLL ICs.

The PLL contribution to the phase noise (PN<sub>PLL</sub>) can be summarized as the root-mean-square addition of two components:  $PN_{PD}$  a component determined by the phase detector comparison frequency, and  $PN_{Baker}$  a flicker component independent of the phase detector comparison frequency given in Eqs. 1 and 2:  $PN_{Baker}$  (4.1). But 1.1 and 2:  $PN_{Baker}$  (4.1). But 1.1 and 2:  $PN_{Baker}$  (4.1). But 1.1 and 2:  $PN_{Baker}$  (4.1).

$\begin{array}{l} PN_{flicker}(dBc/Hz) = PLL_{flicker} + 20log_{10}(f_{VCO} \\ - \ 10log_{10}(\ f_{Offset}) \ (with \ frequencies \ in \ Hz) \end{array} \label{eq:pnflicker}$  (4)

In these equations, the  $PLL_{pOA}$ , and  $PLL_{blacker}$  are determined by the PLL design choices, and usually provided by the PLL manufacturer, where  $f_{VCO}$  is the output frequency of the oscillator,  $f_{PO}$  is the phase detector comparison frequency, and  $f_{Obset}$  is the frequency offset from the carrier used when estimating the phase noise. The noise added by the PLL circuit will then be:

$PN_{PLL} [dBc/Hz] = 10 * log_{10} [10 (PN_{PD}/10) + 10 (PN_{flicker})/10)]$  (5)

Applical case with  $PLL_{EQM} = -220$ ,  $PLL_{eQM} = -220$ ,  $PLL_{eQM} = -230$ , PCDMH2, and  $f_{OBm} = 10$  kHz will result in  $PN_{PD} = -220 + 188 - 70 = -92$ ;  $PN_{Backer} = -250 + 198 - 40$  = -92, and the resulting  $PN_{LL} = -80$  dBc. This is 26 dB higher than the -115 dBc/Hz. contributed by the crystal oscillator considered above. For this circuit, setting the PLL bandwidth to about 20 kHz will result in the best phase-noise performance for any offset frequency. For an integer PLL where frequency division is limited to integer numbers, the output frequency could only be set in 10-MHz increments

This is a serious limitation, since many applications require a smaller step size, say I Hz to 10 kHz. For an ideal noise floor of -174 dBc/Hz with a 1.kHz comparison frequency, at 8 GHz that noise multiplied results in a -36 dBc/Hz PLI. noise floor. Even if such noise would be acceptable, the PLI. loop bandwidth should be set to about 100 Hz, subjecting the design to high level microphonics effects. Such a small loop bandwidth will also greatly increase the setting time of the PLI.

Settling time is determined by loop bandwidth and the time needed to charge the loop filter's capacitors with limited charge pump current. A design with a 10kHz loop bandwidth may use a 1-µF capacitor in the loop. With a charge pump current of 5 mA, approximately 5 ms is needed to charge a 1-µF capacitor to 25 V. Again, with a 10-kHz loop bandwidth, the minimum comparison frequency at the phase detector's input would be about to lot kHz, limiting the step size to the same

100 kHz. This comparison frequency will ideally result in an 8-GHz output having a loop noise floor of -76 dBc/Hz when using a crystal oscillator with -174 dBc noise floor.

A fractional-N PLL helps overcome some of these limitations, dynamically changing the feedback ratio. As a result, the average divide ratio becomes a fractional number. The major advantage of this technique is that the phasedetector comparison frequency does not change with step size.

This is a block diagram of a typical fast-switching DDS-based frequency synthesizer.

## DDS-BASED SYNTHESIZERS

In the following example, the output frequency is 7999.9 MHz and the reference requency is 10 MHz. The feedback divider divides 99 times out of 100 by 800 and divides 1 out of 100 times by 799. The average division ratio is 799.9, the output frequency is 7999.9 MHz and the phase detector comparison frequency is 10 MHz. The PLL phase noise is  $PN_{\rm PLL} = -89$  dBc/Hz, as calculated above, a major advantage over an integer PLL which ideall would only give

The drawback of this technique is the introduction of the fractional spurious product in the spectrum that has a repetition rate determined by the period nearly of the variety of variety

-76 dBc/Hz

amplitude is to be expected with this anproach, and the PLL loop filter bandwidth must be reduced to attenuate the spurious content to an acceptable level. A PLL bandwidth of 10 kHz will impose a practical limit of about 100 kHz on the step size. Spurious generated by the fractional-N PLL is caused by the inability of digital frequency dividers to position the transitions of the feedback clock with absolute accuracy in time. The time resolution of the transition is equal with the period of the clock provided at the divider's input. A DDS can overcome this limitation by adding a level of analog control to the transition. By generating an analog sinusoidal wave, the position of the zero-crossings of the sine wave can be controlled with high accuracy, resulting in close-to-carrier spurious levels at -100 dBc/Hz. It is worth mentioning that the DDS, or any fractional frequency divider, will exhibit a high spurious case when the input frequency of the

DDS is close to a rational multiple of the output frequency. This spurious is called "integer boundary spur" and is particularly difficult to eliminate.

For frequency synthesis purposes, the DDS circuit could be considered as a low-noise frequency divider. The output frequency of this DDS divider is described by:  $f_{DDS} = (N/2^k)f_{Clk} \quad \mbox{(6)}$  where:

$$\begin{split} f_{DDS} = & \text{the DDS output frequency;} \\ N = & \text{a digital number represented with k-bit resolution;} \text{ and} \end{split}$$

$f_{\text{Clk}}$  = the frequency of the DDS's input clock.

In practice,  $f_{\rm Clk}$  is limited to  $0.4f_{\rm Clk}$ , or about 400 to 1000 MHz, when using modern DDS ICs with  $f_{\rm Clk}$  as large as 1 to 2.5 GHz. The resolution of the output frequency is typically set to 32 or 48 b.

The availability of low-cost, low-noise VCOs <sup>27</sup> clears the way for small, low-noise synthesizers. Part of using these sources

involves modeling surfaceacoustic-wave (SAW) resonators under large-signal drive conditions for better insights about noise dynamics of close-in phase noise: then, manufacturable methods for producing highpurity and temperature-stable oscillators in chip form can be developed. Figure 6 is a block diagram for a configurable userdefined multi-band low-noise VCO with 2-to-4-GHz/4-to-8-GHz/5-to-10-GHz/6-to-12-GHz tuning range. It is compact (0.3 x 0.3 x 0.08 in.), operates at 12 mA and 5 V, and exhibits phase

6. This is a block diagram of a typical low-noise, wideband VCO measuring 0.3 x 0.3 in. (See ref. 27.)

offset 1 MHz from the carrier frequency 2 GHz<sup>27</sup> The DDS-based model KMTS2500-200800 synthesizer using highperformance adaptive dynamic modecoupled, low-phase-noise VCO using

noise of typically -135 dBc/Hz

patented techniques. 13-26

A low-noise PLL multiplies a reference frequency to the maximum frequency allowed by the DDS circuit. The DDS output signal is then filtered and provided as a reference to a secondary PLL that will multiply the frequency to the desired range. Depending on design choices, the phase-noise performance may be limited by the primary PLL, the DDS circuit, or the secondary PLL However, the spurious performance is determined by the frequency multiplication and division implemented by the

With this module, it is desired to generate 2000.001 MHz using a 10-MHz reference. The low-noise PLL multiplies the 10-MHz clock to 1 GHz, and the DDS uses this signal to produce the

PLL circuits and the DDS.

62.50003125 MHz required by the secondary PLL. Strong integer boundary spurious products may be noticed at this point in

(continued on p. 154)

the DDS output at 500 Hz offset from the ~62.5-MHz carrier. That 500-Hz spurious product will be amplified by 30 dB and would be practically impossible to filter out from the 2.000001-GHz output signal. The KMTS2500-200800-10 employs a proprietary algorithm that selects the best combination of divide ratios, avoiding spurious conditions.

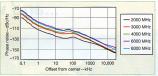

The compact synthesizer module can generate 2-to-8-GHz outputs with a typical phase noise of -97 dBc/Hz offset 10 kHz from the carrier, and typical spurious performance of -50 dBc. Figure 7 shows the typical phase-noise performance of the synthesizer for 2-, 4-, 6-, and 8-GHz outputs. The topology can be used at standard and custom frequencies for X and Ka band applications using low noise VCO,27 saving the complexity and the compromised reliability of other reference source solutions. Finally, the table offers a summary of these results. MWF REFERENCES

1. K. Ma, K. Liang, J. Zhang, and R.M. Jayasuriya, "2-16 GHz microwave synthesizer for wideband software-defined radio system," IEEE European Microwave Conference (EuMC), 2009, pp. 1900-

2. U.L. Rohde and A.K. Poddar, "Shrinking VCO enables configurable Synthesizers," European Microwave Conference (EuMC), October 2009, pp.

1203-1206 3. A. Sadeka and M. Martin, "A Low Jitter, Wideband Frequency Synthesizer with Process Tolerant Auto-Callibration Techniques," IEEE Radio and Wireless

Symposium, January 2007, pp. 353-356 4. U.L. Rohde, Microwave and Wireless Synthesizers: Theory and Design, 1st ed., Wiley-Interscience,

Singapore, 1997 Paul P. Sotiriadis, "Exact Spectrum and Time-Domain Output of Flying-Adder Frequency

Synthesizers," IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control, Vol. 57, No. 9, September 2010.

U.L. Rohde and A.K. Poddar, "A Digital Frequency Synthesizer Using Adaptive Mode-Coupled Resonator Mechanism for Low Noise and Low Jitter Applications," IEEE International Symposium on Circuits and Systems (ISCAS), May 15-18, 2011,

Brazil, pp. 414-417.

7. D. Calbaza and Y. Savaria, "A direct digital periodic synthesis circuit," IEEE Journal of Solid-State Circuits, Vol. 37, No. 8, August 2002, pp. 1039-1045

B. U.L. Rohde and A.K. Poddar, "A Novel Low Cost High Performance Synthesizer," Proceedings of the IEEE European Microwave Conference (EuMC), October 2011, pp. 200-203.

9. J. Browne, Fast Synthesizers serve EW systems," Microwave & RF, March/April 2010 Defense Electronics Supplement

10. U.L. Rohde and A.K. Poddar, "A Novel High

7. These plots show the phase noise of the DDS-based model KMTS2500-200800-10 synthesizer at four different carrier frequencies.

| Sum                                 | nmarizir               | ng the K<br>phase | MTS250<br>noise. | 0-20080 | 10's    |

|-------------------------------------|------------------------|-------------------|------------------|---------|---------|

|                                     | Output frequency (GHz) |                   |                  |         |         |

|                                     |                        |                   |                  |         | 8       |

| Offset from<br>the carrier<br>(kHz) | Phase noise (dBc/Hz)   |                   |                  |         |         |

| 0.1                                 | -89.88                 | -83.64            | -81.56           | -76.32  | -77.42  |

| 1                                   | -111.52                | -104.51           | -102.73          | -97.01  | -98.70  |

| 10                                  | -123.82                | -116.66           | -114.90          | -109.51 | -111.04 |

| 100                                 | -127.35                | -119.99           | -117.16          | -114.05 | -113.66 |

| 1000                                | -137.05                | -133.81           | -131.95          | -127.50 | -126.04 |

| 10,000                              | -153.82                | -153.78           | -151.36          | -145.79 | -144.16 |

Frequency Synthesizer Using Adaptive Injection Mode-Coupled VCSO for Low Jitter and Low Noise Applications," Proceedings of the 2011 Joint Conference of the IEEE International Frequency Control Symposium & European Frequency and Time Forum, May 2010, pp. 452-457. 11. U.L. Rohde, A.K. Poddar, and G. Boeck, Modern

Microwave Oscillators for Wireless Applications: Theory and Optimization, Wiley, NY, 2005. W. Egan, Frequency Synthesis by Phase Lock, Wiley, Hoboken, NJ, 2000.

13. U.L. Rohde and A.K. Poddar, "Wideband

voltage controlled oscillators employing evanescent mode coupled resonators," United States Patent No. 7,180, 381 February 20, 2007. 14. U.L. Rohde, A.K. Poddar, and R. Rebel, "Integrated Low Noise Microwave Wideband Push-

Push VCO," United States Patent No. 7,088189, August 2006. 15. U.L. Rohde and A.K. Poddar, "User-Definable Thermal Drift Voltage Controlled Oscillator," United States Patent No. 7, 265,642 B2, September 4,

2007 16. U.L. Rohde and A.K. Poddar, "Low Thermal Drift Tunable Frequency Voltage Controlled Oscillator, United States Patent No. 7, 262,670 B2, August

28 2007 17. U.L. Rohde and A.K. Poddar, "Tunable Oscillator," United States Patent No. 7, 292,113,

November 6, 2007. 18. U.L. Rohde and A.K. Poddar, "Tunable Frequency, Low Phase Noise and Low Thermal Drift Oscillator," United States Patent No. 7196591, March 2007

19. U.L. Rohde and A.K. Poddar, "Low Noise, Hybrid Tuned Wideband Voltage Controlled Oscillator," United States Patent No. 7,365,612 B2, April 29, 2008 20. U.L. Rohde and A.K. Poddar, "Tunable Frequency, Low Phase Noise and Low Thermal Drift Oscillator," United States Patent No. 7, 545, 229, June 9, 2009 21. U.L. Rohde and A.K. Poddar, "User-Definable, Low Cost, Low Phase Hit and Spectral Pure Tunable Oscillator, United States Patent No. 7,586,381, September 08, 2009.

22. U.L. Rohde and A.K. Poddar, "User-Definable, Low Cost, Low noise, and phase hit insensitive multi-octave-band tunable oscillator, Phase Hit and Spectral Pure Tunable Oscillator," United States Patent No. 7,605,670, October 20, 2009.

23. U.L. Rohde and A.K. Poddar, "Low Noise and Low Phase Hits Tunable Oscillator," United States Patent No. 7,636, 021, December 22, 2009.

24. U.L. Rohde and A.K. Poddar Wideband voltage controlled oscillators employing evanescent mode No. 2,563, 174, July 21, 2009. 25. U.L. Rohde and A.K. Poddar.

User-Definable Thermal Drift Voltage Controlled Oscillator," Canadian Patent No. 2.548.317. April 21. 2009. 26. U.L. Rohde and A.K. Poddar, Integrated Low Noise Microwave Wideband Push-Push VCO," Canadian Patent No. 2,548,311, April 14, 2009.

27. Synergy Microwave Corp, low-noise VCOs product data sheet, available at www.synergymwave.com. 28. P.S. (Paul) Khanna, "Microwave Oscillators: The State of The Technology," Microwave Journal, April

Technology," Microwave Journal, Ar 2006, pp. 22-42. 29. A. Chenakin, "Building Microwave Frequency Synthesizer Part-2: Component Selection," Hig Frequency Electronics, 2008, pp. 18-26 G. Gonzalez, Foundations of Oscillator Circuit, Artech House,

London, 2007, Chap. IV. 31. A. Grebennikov, RF and Microwave Transistor Oscillator Design, Wiley,

London, 2007 32. J.K.A. Everard and L. Zhou. "Non Linear Effects in varactor tuned resonators," IEEE Transactions on Ultrasonics Ferroelectrics and Frequency Control,

Vol. 53, No. 5, May 2006, pp. 853-861.

33. T. Ohira and K. Araki, "Active Q factor and equilibrium stability formulation for sinusoidal oscillators," IEEE Transactions on Circuits & Systems II, Vol. 54, No.9, 2007-2008, pp. 810-814

34. J.C. Nallatamby, M. Prigent, M. Camiade, and J.J. Obregon, "Extension of the Leeson formula to phase noise calculation in transistor oscillators with complex tanks," IEEE Transactions on Microwave

Theory & Techniques, Vol. 51, No. 3, March 2003, pp. 690-696 35. W. Egan, Frequency Synthesis by Phase Lock,

Wiley, Hoboken, NJ, 2000. 36. S. Pamarti and S. Delshadpour, "A spur elimination technique for phase interpolation-based fractional-N PLIs "IFFE Transactions on Circuits &

Systems I, Regular Papers, Vol. 55, No. 6, July 2008, systems I, Regular Papers, Vol. 55, No. 6, July 2008, pp. 1639-1647.

37. Y. Sun, et al., "Dual-path LC VCO design with partitioned coarsetuning control in 65nm CMOS," IEEE MWCL, March 2010.

38. X. Yu, et al., "A fractional-N frequency synthesizer

with customized noise shaping for WCDMA/HSDPA applications," IEEE Journal of Solid-State Circuits,

Vol. 44, August 2009, pp. 2193-2201. 39. T. Wu, P. Hanumolu, K. Mayaram, and U. Moon, "A 4.2-GHz PLL frequency synthesizer with an adaptively tuned coarse loop," in Proceedings of

adaptively tuned coarse loop," in Proceedin the IEEE CICC, September 2007, pp. 547-550 40. A. Chenakin," Frequency Synthesis: Current Solutions And New Trends," Microwave Journal, May 2007, pp. 256-266. 41. J. Browne, "Frequency Synthesizers Tune Communication Systems," Microwaves & RF,

March 2006.