# Introduction to Modern Signal Generation; from Analog to Digital: Needs, Advantages, Disadvantages and "Solutions"

Prof. Dr.-Ing. habil. Ulrich L. Rohde, Member of the Faculty of Informatics, Cyber Security, University of the Department of Defense, Federal Republic of Germany, Munich

#### **Incentives:**

In the age of wideband modulation capabilities, our "good old" signal generators maybe nice and low noise, but unable to generate the needed modern signals. On the other hand they are a good starting topic to explain the circuitry of analog signal generators, even their complexity and how and why modern signal generators evolved. This also needs an introduction to frequency synthesis.

The traditional communication essentially took place from point to point and starting with AM modulation, for broadcast later with FM modulation, evolved to single side-band suppressed carrier modulation (SSB). For the most reliable communication, MORSE code was invented and in many ways is still used and actually the forerunner of digital modulation. To assess today's problems here is an introductory chapter of what really happens. [1-6]

#### The Radio Channel and Modulation Requirements

#### Introduction

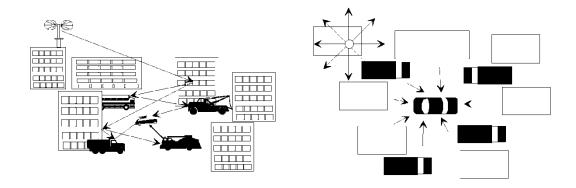

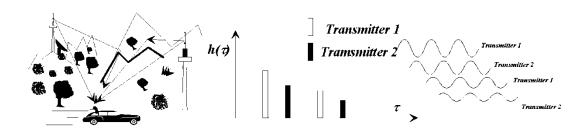

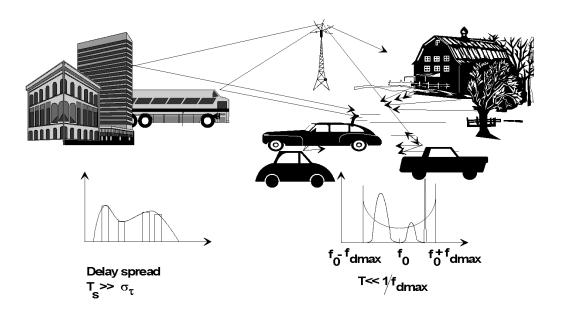

The transmission of information from a fixed station to a mobile is considerably influenced by the characteristics of the radio channel. The RF signal arrives at the receiving antenna not only on the direct path but is normally reflected by natural and artificial obstacles in its way. Consequently the signal arrives at the receiver several times in the form of echoes which are superimposed on the direct signal. (See Figure: 1). This superposition may be an advantage as the energy received in this case is greater than in single-path reception. This feature is made use of in the DAB single-frequency network. However, this characteristic may be a disadvantage when the different waves cancel each other under unfavorable phase conditions. In conventional car radio reception this effect is known as fading. It is particularly annoying when the vehicle stops in an area where the field strength is reduced because of fading (for example, at traffic lights). Additional difficulties arise when digital signals are transmitted. If strong echo signals (compared to the directly received signal) arrive at the receiver with a delay in the order of a symbol period or more, time-adjacent symbols interfere with each other. In addition, the receive frequency may be falsified at high vehicle speeds because of the Doppler effect so that the receiver may have problems to estimate the instantaneous phase in the case of angle-modulated carriers. Both effects lead to a high symbol error rate even if the field strength is sufficiently high. Radio broadcasting systems using conventional frequency modulation are hardly affected by these interfering effects. If an analog system is replaced by a digital one which is expected to offer advantages over the previous system, it has to be ensured that these advantages--for example, better AF S/N and the possibility to offer supplementary services to the subscriber--are not at the expense of reception in hilly terrain or at high vehicle speeds because of extreme fading.

Figure 1: Mobile receiver affected by fading [1]

For this reason a modulation method combined with suitable error protection has to be found for mobile reception in a typical radio channel, which is immune to fading, echo and Doppler effects. [1]

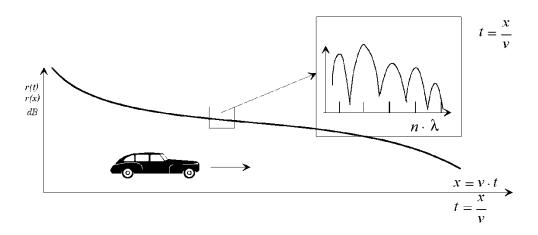

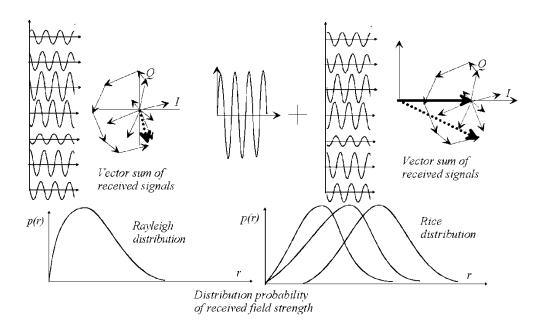

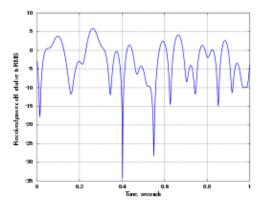

With a view to this, more detailed information on the radio channel is required. The channel can be described by means of a model. In the worst case, which may be the case for reception in built-up areas, it can be assumed that the mobile receives the signal on several indirect paths but not on a direct one. The signals are reflected for example by large buildings; the resulting signal delays are relatively long. In the vicinity of the receiver these paths are split up into a great number of subpaths; the delays of these signals are relatively short. These signals may again be reflected by buildings but also by other vehicles or natural obstacles like trees. Assuming the subpaths being statistically independent of each other, the superimposed signals at the antenna input cause considerable time- and position-dependent field-strength variations with an amplitude obeying the Rayleigh distribution (Figures 2 and 3).[1]

Figure 2: Receive signal as a function of time or position [1]

Figure 3: Rayleigh and Rice distribution [1]

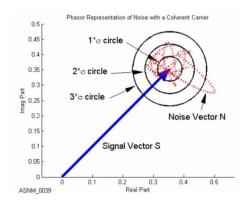

Additive white Gaussian noise **(AWGN)** is a basic noise model used in Information theory to mimic the effect of many random processes that occur in nature. The modifiers denote specific characteristics: Additive because it is added to any noise that might be intrinsic to the information system.

Additive white Gaussian noise - Wikipedia https://en.wikipedia.org/wiki/Additive\_white\_Gaussian\_noise

Figure 3a: Additive white Gaussian noise

Figure 3b: Rayleigh Distribution

**Rayleigh fading** is a statistical model for the effect of a propagation environment on a radio signal, such as that used by wireless devices

# Rayleigh fading – Wikipedia https://en.wikipedia.org/wiki/Rayleigh\_fading

If a direct path is received in addition, the distribution changes to the Rice distribution and finally, when the direct path becomes dominant, the distribution follows

Gaussian distribution with the field strength of the direct path is being used as the center value.

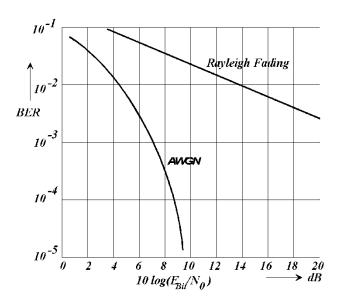

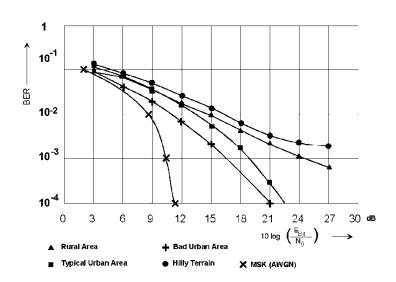

In a Rayleigh channel the bit error rate increases dramatically compared to the BER in an AWGN channel produces (Figure 4).

Figure 4: BER in a Rayleigh channel [1]

#### **Channel Impulse Response**

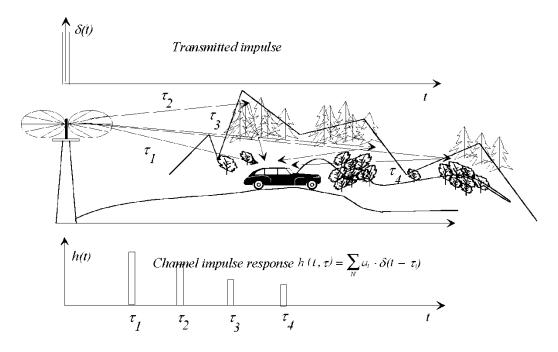

This scenario can be demonstrated by means of the channel impulse response. Let's assume that a very short pulse of extremely high amplitude (in the ideal case a Dirac pulse  $\delta(t)$ ) is sent by the transmitting antenna at a time  $t_0 = 0$ . This pulse arrives at the receiving antenna direct and in the form of reflections with different delays  $\tau_i$  and different amplitudes because of path losses. The impulse response of the radio channel is the sum of all received pulses (Figure 5). Since the mobile receiver and also some of the reflecting objects are moving, the channel impulse response is a function of time and of delays  $\tau_i$ ; that is, it corresponds to

$$h(t,\tau) = \sum_{N} a_{i} \delta(t - \tau_{i})$$

(1)

This shows that delta functions sent at different times *t*, causes different reactions in the radio channel.

Figure 5: Channel impulse response [1]

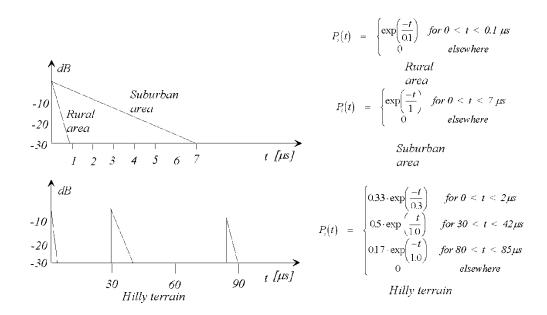

In many experimental investigations different landscape models with typical echo profiles were created.

The most important are:

- rural area (RA)

- typical urban area (TU)

- bad urban area (BA)

- hilly terrain (HT)

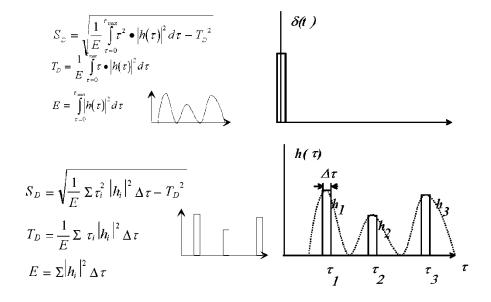

The channel impulse response informs on how the received power is distributed to the individual echoes. A parameter, the "delay spread" can be calculated from the channel impulse response, permitting an approximate description of typical landscape models (Figure 6). [1]

Figure 6: Calculation of delay spread [1]

The delay spread also roughly informs on the modulation parameters carrier frequency, symbol period and duration of guard interval, which have to be selected in relation to each other. If the receiver is located in an area with a high delay spread (for example, in hilly terrain), echoes of the symbols sent at different times are superimposed when broadband modulation methods with a short symbol period are used. In the case of DAB, this problem is aggravated by the use of single-frequency networks. An adjacent transmitter emitting the same information on the same frequency has the effect of an artificial echo (Figure 7). [1]

Figure 7: Artificial and natural echoes in the single-frequency network [1]

A constructive superposition of echoes is only possible if the symbol period is much greater than the delay spread. The following holds:

$$T_s > 10T_d \tag{2}$$

This has the consequence that relatively narrowband modulation methods have to be used. If this is not possible, channel equalizing is required.

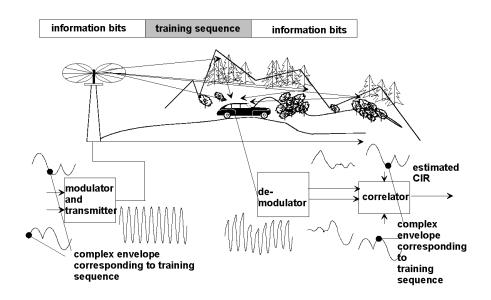

For the channel equalizing a continuous estimation of the radio channel is necessary. The estimation is performed with the aid of a periodic transmission of data known to the receiver. In networks according to the GSA standards a mid-amble consisting of 26 bits--the training sequence--is transmitted with every burst. The training sequence corresponds to a characteristic pattern of I/Q signals that is kept in a memory in the receiver. The baseband signals of every received training sequence are correlated with the stored ones. From this correlation the channel can be estimated, the properties of the estimated channel will then be fed to the equalizer (Figure 8).

Figure 8: Channel Estimation [1]

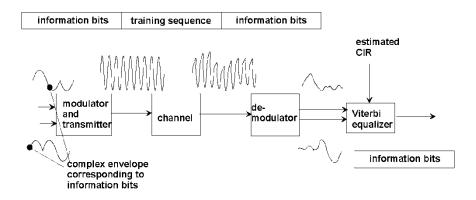

The equalizer uses the Viterbi algorithm (maximum sequence likelihood estimation) for the estimation of the phases which most likely have been sent at the sampling times. From these phases the information bits are calculated (Figure 9). A well designed equalizer then will superimpose the energies of the single echoes constructively, so that the result in an area, where the echoes are not too much delayed, delay times up to 16  $\mu$ s have to be tolerated by a receiver, are better than in an area with no significant echoes (Figure 10).

Figure 9: Channel equalization [1]

Figure 10: BERs after the channel equalizer in different areas [1]

Remaining bit errors are eliminated using another Viterbi decoder for the at the transmitter convolutionally encoded data sequences.

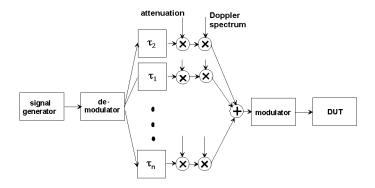

The ability of a mobile receiver to work in a hostile environment such as the radio channel with echoes must be proven. The test is performed with the aid of a fading simulator. The fading simulator simulates different scenarios with different delay times and different Doppler profiles. A signal generator generates undistorted I/Q modulated RF signals which are downconverted into the baseband. Here the I/Q signals are digitized and split into different channels where they are delayed and attenuated and where Doppler effects are superimposed. After combination of these distorted signals at the output of the baseband section of the simulator these signals modulate the RF carrier which is the test signal for the receiver under test (Figure 11).

Figure 11: Fading simulator [1]

To make the tests comparable GSM recommends typical profiles; for example:

- Rural Area (RAx)

- Typical Urban (TUx)

- Hilly Terrain (HTx)

where number and strengths of the echoes and the Doppler spectra are prescribed (Figure 12).

Figure 12: Typical landscape profiles [1]

#### **Doppler Effect**

Since the mobile receiver and some of the reflecting objects are in motion, the receive frequency is shifted because of the Doppler Effect. In the case of single-path reception this shift is calculated as follows:

$$f_d = \frac{v}{c} f_c \cos \alpha \tag{3}$$

where v = speed of vehicle

c = speed of light

f = carrier frequency

$\alpha$  = angle between  $\nu$  and the line connecting transmitter and receiver

In the case of multipath reception the signals on the individual paths arrive at the receiving antenna with different Doppler shifts because of the different angles  $\alpha_i$ , and the receive spectrum is spread. Assuming an equal distribution of the angles of incidence, the power density spectrum can be calculated as follows:

$$P(f) = \frac{1}{\pi} \frac{1}{\sqrt{f_d^2 - f^2}} \text{ for } |f| < |f_d|$$

(4)

where  $f_d$  = maximum Doppler frequency.

where  $f = \max$ . Doppler frequency

Of course, other Doppler spectra are possible in addition to the pure Doppler shift described above; for example, spectra with a Gaussian distribution using one or several maxima. A Doppler spread can be calculated from the Doppler spectrum analogously to the delay spread (Figure 13). [1]

Figure 13: Doppler spread [1]

## **Some Examples:**

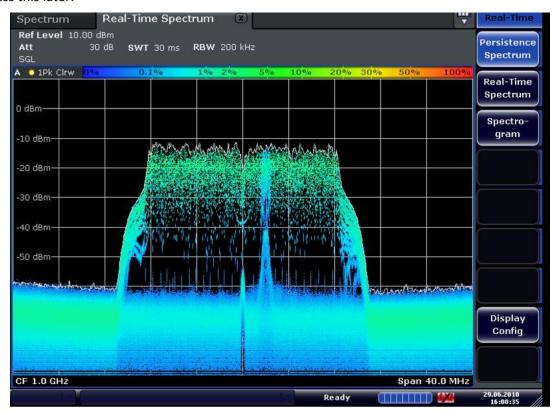

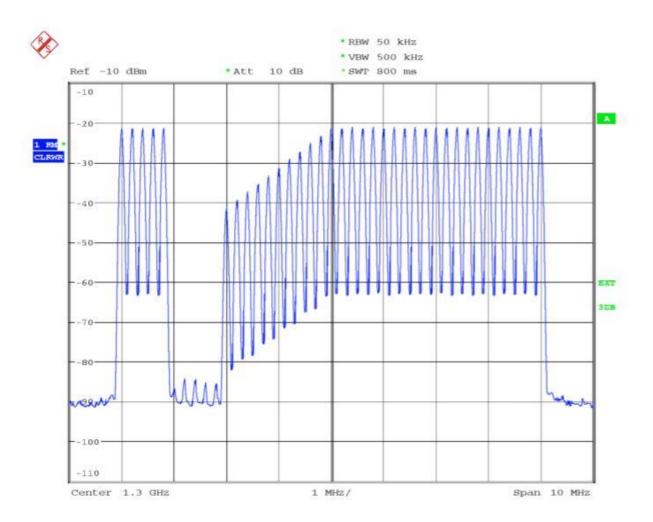

Figure 14 shows a complex waveform which is needed for testing modern receivers, such as Software Defined Radios. Signal generators that can handle this are using a combination of many techniques. I will address this later.

Figure 14: A Wi-Fi Wideband Signal Including a Discrete Carrier

Figure 15: Example of multicarrier CW, with different carrier powers and some carriers switched off in the left half of the spectrum, I/Q level 0.5V (meas.). This is needed for advanced receiver testing

#### Why this presentation:

As seen above, the modern signal generator must be able to simulate these effects like fading, Doppler Effect, multi-pass signal, to really test the implemented system and algorithm (receiver).

#### Part I:

#### The Analog Signal Generator:

The next part will cover this, and then we will move to the digital signal generation in the part two. At the end we will look at hybrid combinations.

So now let us take a look at today's signals as we meet them when doing signal detection and analysis.

It is obvious that the generation of such a really wide band signal requires quite some modulation design techniques.

These modern generators are also used for performance testing of "Software Defined Radio's"

And it is not surprising that sometimes the internal numerically controlled oscillator, DDS based, close in phase noise, maybe better than the test generator.

The book Communications Receivers, see below, has a dedicated chapter about testing the performance of both analog and digital receivers.

Figure 16: Communication Receivers – Principle and Design

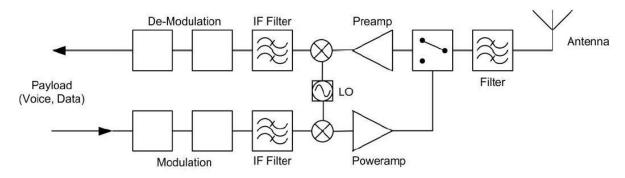

While this book title (Figure 16) says receivers, a short part of it addresses the transmitter part.

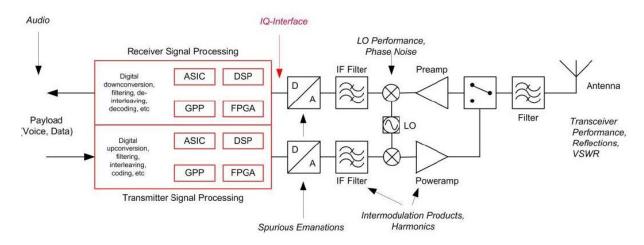

Here is a block diagram of an analog transceiver and the earlier signal generators were designed to allow the measurements of the receiver part.

# From analog radios to software defined radio

Figure 17: Conventional analog (hardware) radio (simplified)

Figure 17 provides a block diagram of a classic hardware radio, split into the receiver and the transmitter branches. The received signal is first filtered and preamplified. It is then downconverted from the carrier frequency to an intermediate frequency (this can take place over several steps). The signal is filtered once again and then demodulated. The (de)modulation block can be either analog or digital.

Also, here is a short list of parameters of interest to be determined for an analog radio. What's the difference? It's the determination of the large signal dynamic range, which will be different for SDRs.

| Receiver tests                                      |

|-----------------------------------------------------|

| Receiver sensitivity and associated characteristics |

| Demodulation characteristics                        |

| Dynamic sensitivity and desensitization             |

| Spurious response and IF rejection                  |

| ntermodulation response (out of band)               |

| Blocking                                            |

| Oscillator emission                                 |

| Cross modulation rejection                          |

| Receiver response time                              |

Over the past decades huge progress has been made in developing new types of oscillators and amplifiers and modulation applications, both amplitude and frequency related and a combination of both.

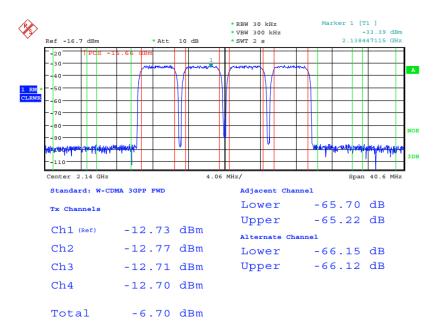

This 4 channel test is a real life requirement, which the traditional generators cannot handle. This can only be done with I/Q based advanced Vector Signal Generator using arbitrary wave generation.

The following is an example of how such a signal looks like.

Figure 18: Measured ACPR for a 3GPP four-carrier signal with test model 1, 64 DPCH on each carrier (baseband gain: +3dB)

I will now show the development from simple analog based signal generators using different resonators, to synthesizers with still analog modulation capabilities, to "direct digital synthesizer with arbitrary waveform generators" to finally modern hybrid synthesizers that combine the best of both worlds. Also opto electrical applications will be considered

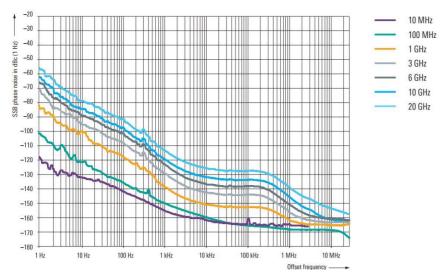

Signals need to be stable, pure (minimal spurious signals), clean (minimal phase noise) and of sufficient output power.

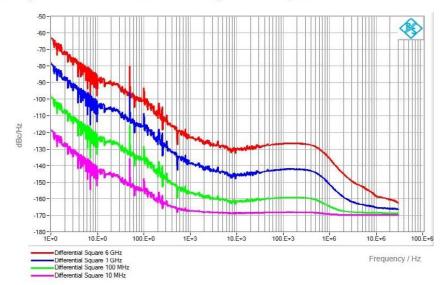

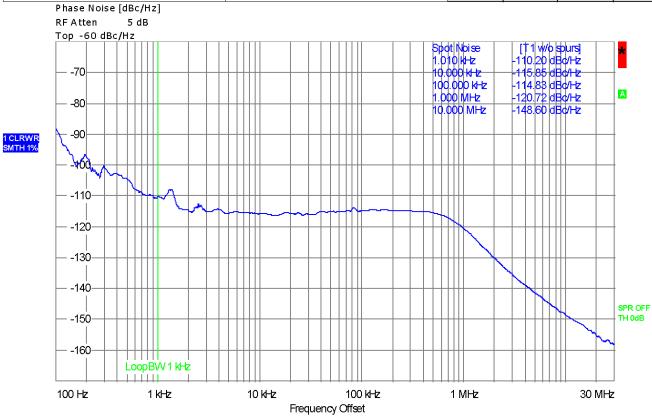

The following shows the measured phase noise of the best analog synthesizer currently on the market (2018)

Figure 19: The measured phase noise of a modern clock synthesized generator

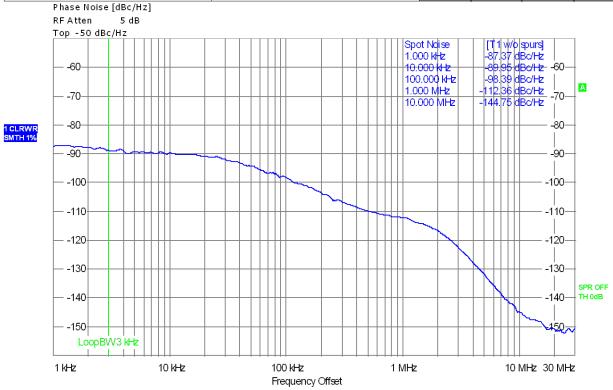

# **Functions and Features**

Clock Synthesizer - with enhanced close in phase noise option

Figure 20: R&S SMA100 Functions and Features – Clock Synthesizer – with enhanced close-in phase noise option

Figure 21: R&S SMA 100B

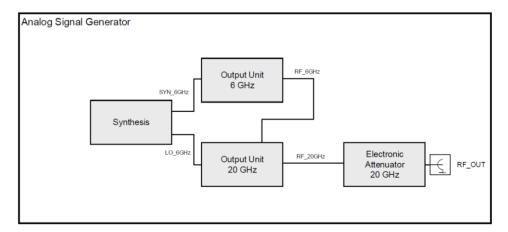

These performance capabilities in an analog signal generator are found in the new R&S SMA 100B. This covers 8 kHz to above 20GHz, depending on the options.

In the "digital" signal generation section the tools and tricks will be described that are needed.

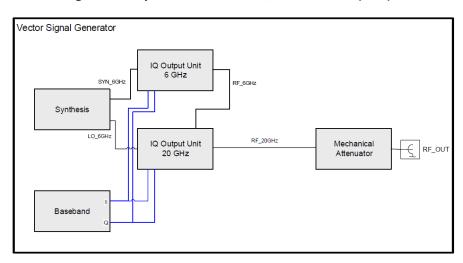

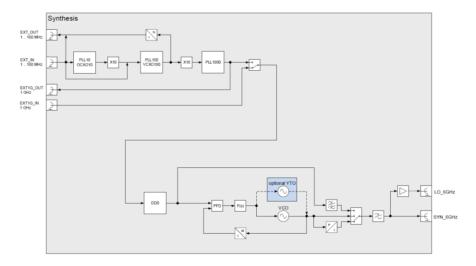

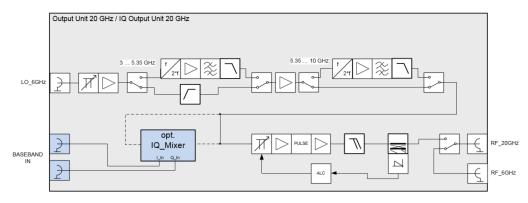

If all combined, is now the resulting signal generator a "Vector Signal Generator" useful for a host of applications, and covers the range upto 40GHz.

Figure 22: R&S Vector Signal Generator - SMW200A

More details about signal generation and synthesizers will be in my forthcoming book, Figure 23.

Figure 23: Microwave and Wireless Synthesizers – Theory and Design

Since the oscillator is the key part of any signal generator, besides having a power supply, AM and FM modulator, buffer/output amplifier, output filter is needed.

#### Now some technical details about oscillators:

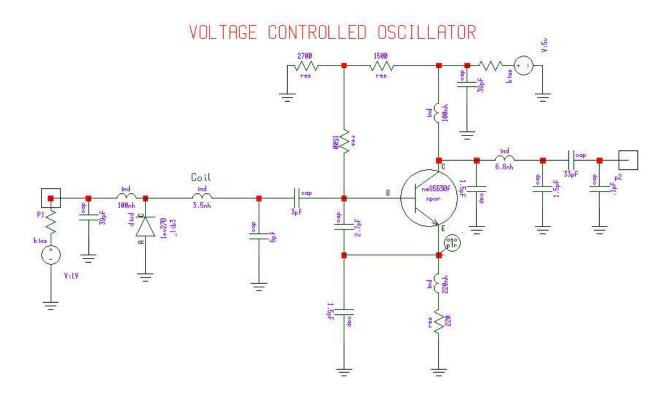

The majority of LC based oscillators are based on the Colpitts oscillator design.

Figure 24: Schematic diagram form of the linear model of an oscillator [3]

Figure 24 is the schematic of a voltage-controlled Colpitts-type oscillator. The Colpitts circuit is recognized by the capacitive feedback network comprised of the capacitors connected between base and emitter and emitter to ground. For frequency tuning, a tuning diode, varactor diode, has been added.

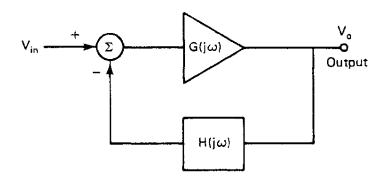

Figure 25 shows, in block diagram form, the linear model of an oscillator. It contains an amplifier with frequency-dependent forward loop gain  $G(j\omega)$  and a frequency-dependent feedback network  $H(j\omega)$ . This network is typically the resonator which will determine the oscillation frequency. Its figure of merit Q should be made as high as possible.

Figure 25: Block diagram of an oscillator showing forward and feedback loop components [3]

The output voltage is given by

$$V_o = \frac{V_{\rm in}G(j\omega)}{1 + G(j\omega)H(j\omega)} \tag{5}$$

For an oscillator, the output  $V_o$  is nonzero even if the input signal  $V_{in} = 0$ . This can only be possible if the forward loop gain is infinite (which is not practical), or if the denominator

$$1 + G(j\omega)H(j\omega) = 0 \tag{6}$$

at some frequency  $\omega_o$ . This leads to the well-known condition for oscillation (the *Nyquist criterion*), where at some frequency  $\omega_o$

$$G(j\omega_{o})H(j\omega_{o}) = -1 \tag{7}$$

That is, the magnitude of the open-loop transfer function is equal to 1:

$$|G(j\omega_{\alpha})H(j\omega_{\alpha})| = 1 \tag{8}$$

and the phase shift is 180°:

$$\arg[G(j\omega_o)H(j\omega_o)] = 180^{\circ}$$

(9)

This can be more simply expressed as follows: if in a negative-feedback system, the open-loop gain has a total phase shift of  $180^{\circ}$  at some frequency  $\omega_0$ , the system will oscillate at that frequency provided that the open-loop gain is unity. If the gain is less than unity at the frequency where the phase shift is  $180^{\circ}$ , the system will be stable, whereas if the gain is greater than unity, the system will be unstable. [3]

This statement is not correct for some complicated systems, but it is correct for those transfer functions normally encountered in oscillator design. The conditions for stability are also known as the *Barkhausen criterion*, which states that if the closed-loop transfer function, is

$$\frac{V_o}{V_{in}} = \frac{\mu}{1 - \mu\beta} \tag{10}$$

where  $\mu$  is the forward voltage gain and  $\beta$  is the feedback voltage gain, the system will oscillate provided that  $\mu\beta$  = 1. This is equivalent to the Nyquist criterion, the difference being that the transfer function is written for a loop with positive feedback. Both versions state that the total phase shift around the loop must be 360° at the frequency of oscillation and the magnitude of the open-loop gain must be unity at that frequency.

#### The Colpitts oscillator in more detail

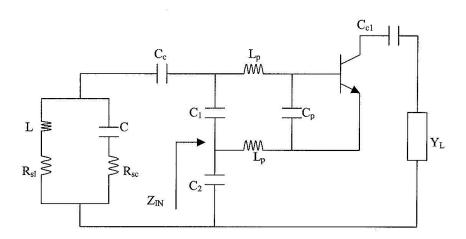

In the practical case, the device parasitics and loss resistance of the resonator will play an important role in the oscillator design. Figure 26 incorporates the base lead-inductance  $L_p$  and the package-capacitance  $C_p$ .

Figure 26: Colpitts oscillator with base-lead inductances and package capacitance,  $C_c$  is neglected [3]

The expression of input impedance is given as [15]

$$Z_{IN}\big|_{pacakage} = -\left[\frac{Y_{21}}{\omega^{2}(C_{1} + C_{p})C_{2}} \frac{1}{(1 + \omega^{2}Y_{21}^{2}L_{p}^{2})}\right] - j\left[\frac{(C_{1} + C_{p} + C_{2})}{\omega(C_{1} + C_{p})C_{2}} - \frac{\omega Y_{21}L_{p}}{(1 + \omega^{2}Y_{21}^{2}L_{p}^{2})} \frac{Y_{21}}{\omega(C_{1} + C_{p})C_{2}}\right]$$

The real part is negative in value and compensates the losses of the tuned circuit, the oscillation will get started. [3][15]

This is the linear approach.

The resulting phase noise can be described by the equation combination of Leeson, Scherer and Rohde contributions as follows [3]:

$$\pounds(f_m) = 10\log\left\{ \left[ 1 + \frac{f_0^2}{(2f_m Q_L)^2 (1 - \frac{Q_L}{Q_0})^2} \right] \left( 1 + \frac{f_c}{f_m} \right) \frac{FkT}{2P_o} + \frac{2kTRK_0^2}{f_m^2} \right\}$$

(11)

where  $f_m$ ,  $f_m$ ,  $f_0$ ,  $f_c$ , f

When adding an isolating amplifier the noise of an LC oscillator is determined by

$$\pounds(f_{m}) = 0.5 \times 10 log \left[ \left( S_{\emptyset}(f_{m}) \right) \right] = 0.5 \times 10 log \left\{ \frac{\left[ a_{R} F_{0}^{4} + a_{E} \left( \frac{F_{0}}{(2Q_{L})} \right)^{2} \right]}{f_{m}^{3}} + \left[ \frac{\left( \frac{2GFkT}{P_{0}} \left( \frac{F_{0}}{(2Q_{L})} \right)^{2} \right)}{f_{m}^{2}} \right] + \left( \frac{2a_{R} Q_{L} F_{0}^{3}}{f_{m}^{2}} \right) + \frac{a_{E}}{f_{m}} + \frac{2GFkT}{P_{0}} \right\}$$

(12)

Where,

G = compressed power gain of the loop amplifier

F = noise factor of the loop amplifier

k = Boltzmann's constant

T = temperature in kelvins

$P_0$  = carrier power level (in watts) at the output of the loop amplifier

$F_0$  = carrier frequency in Hz

$f_m$  = carrier offset frequency in Hz

$Q_L(=\pi F_0 \tau_q)$  = loaded Q of the resonator in the feedback loop

$a_R$  and  $a_E$  = flicker noise constants for the resonator and loop amplifier, respectively.

The problem with this design equation, everyone likes to quote, that it works after the fact. That means the designer does not know the output power, the flicker corner frequency, and the large signal noise figure, and finally as the right part of the equation is the noise from the tuning diode, the value of the equivalent noise resistor R!

If the energy is taken carefully from the resonator the far off phase noise can be as low as -175dBc/Hz below the carrier.

It needs to be noted that the phase noise is proportional to  $\frac{1}{O_r^2}$

There are two additional topics to be considered. The voltage-controlled oscillator (VCO) is used rarely stand alone, but mostly in a PLL system, and followed by a buffer / isolation stage [1]

Unfortunately the ultimate phase noise is determined by the buffer/isolation amplifier.

Most of the resonators in an oscillator can be expressed by an LC equivalent. See the Collpits Oscillator above. Additional typical resonators are crystals, SAW resonators, dielectric resonators, even YIG resonators.

The use of transmission lines instead of LC circuits can improve the noise performance, as shown below.

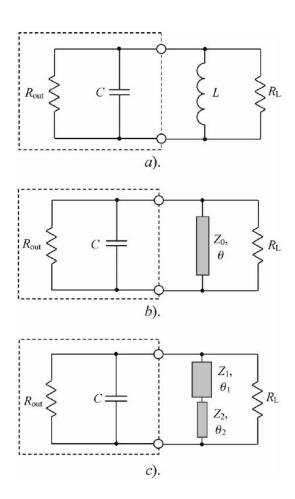

In order to compare the oscillators with lumped and distributed parameters for the purpose of the best phase noise characteristics, it is sufficient to determine the susceptance sensitivity  $S_0$  for each oscillator circuit with equal capacitances. For a simple parallel lumped resonant circuit shown in Figure 27,

$$S_0 = \frac{\partial}{\partial \omega} \left( \omega C - \frac{1}{\omega L} \right) = C \left( 1 + \frac{1}{\omega^2 L C} \right) \Big|_{\omega = \omega_0}$$

(13)

The oscillator parallel resonant circuit with uniform transmission line is shown in Figure 27b. Since the ratio between the transmission line electrical length  $\theta$  and the frequency

Figure 27: Equivalent parallel oscillator resonant circuits with (a) lumped parameters and (b, c) distributed parameters [2]

$\omega$  is defined as

$$\theta = \omega l \sqrt{\varepsilon_{\rm r}}/c \tag{14}$$

where l is the length of the transmission line,  $\varepsilon_r$  is the dielectric permittivity, c is the free-space velocity of light, the following condition is met:

$$\frac{\partial \theta}{\partial \omega} = \frac{\theta}{\omega} \tag{15}$$

Then, by taking into account that  $C = 1/\omega_0 Z_0 \tan \theta$  at resonant frequency, the sensitivity  $S_0$  for the parallel resonant circuit with a lossless uniform transmission line is obtained as

$$S_0 = \frac{\partial}{\partial \omega} \left( \omega C - \frac{1}{Z_0 \tan \theta} \right) = C \left( 1 + \frac{\theta}{\omega C Z_0 \sin^2 \theta} \right) \Big|_{\omega = \omega_0} = C \left( 1 + \frac{2\theta}{\sin 2\theta} \right)$$

(16)

Similarly, the susceptance sensitivity  $S_0$  for the parallel resonant circuit with lossless two-section transmission line of equal section lengths  $\theta_1 = \theta_2 = \theta/2$  shown in Figure 27(c) can be written as

$$S_0 = \frac{\partial}{\partial \omega} \left( \omega C - \frac{1}{Z_1 \tan \frac{\theta}{2}} \frac{1 - M \tan^2 \frac{\theta}{2}}{1 + M} \right) \bigg|_{\omega = \omega_0} = C \left( 1 + \frac{\theta}{\sin \theta} \frac{1 + M \tan^2 \frac{\theta}{2}}{1 - M \tan^2 \frac{\theta}{2}} \right)$$

(17)

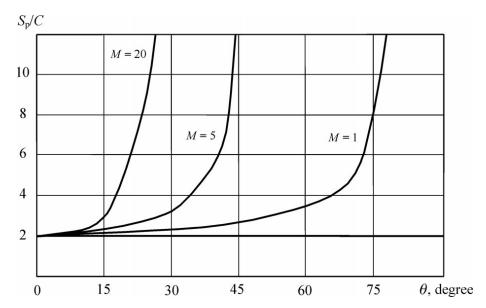

Figure 28 shows the frequency dependencies of the normalized sensitivity  $S_0/C$  for different types of oscillator circuits. For a lumped resonant circuit,  $S_0/C = 2$ , which means that it is independent of frequency. For the resonant circuits with transmission lines, the value of the sensitivity  $S_0$  for a given capacitance C can be increased significantly by an appropriate increase of  $\theta$ . If  $\theta = 40^\circ$ ,  $S_0/C = 2.42$  for the resonant circuit with uniform transmission line,

[2]

Figure 28: Frequency dependencies of the normalized susceptance sensitivity  $S_0/C$  for different characteristic impedance ratio M [2]

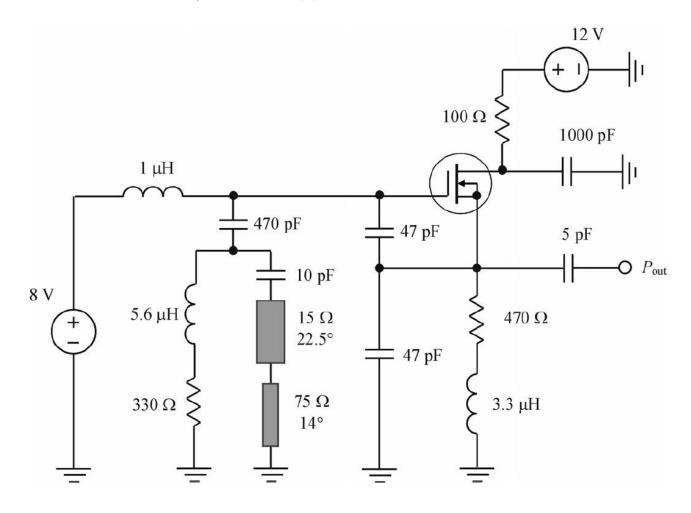

Figure 29: Equivalent circuit of the MOSFET oscillator with two-section line [2]

Whereas the use of the two-section transmission line with M=5 results in  $S_0/C=6.3.5$ . In the case of  $\theta=24^\circ$ , by using of the two-section transmission line with M=20, it is possible to increase the value of  $S_0/C$  by a factor of more than ten. For the same values of  $S_0/C$ , the use of the two-section transmission line with a high value of M enables one to reduce the total electrical length of the transmission line by a factor of three to four.

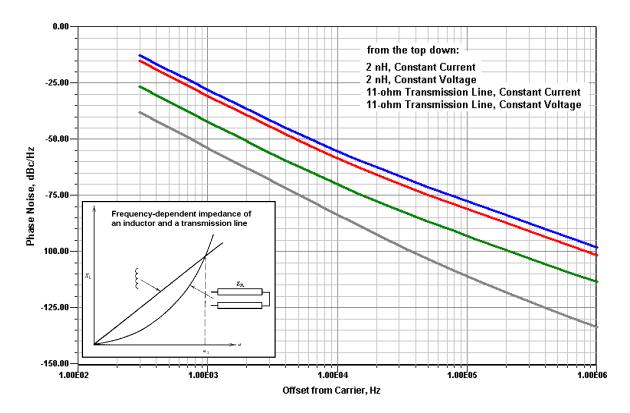

As evidence of how moving from lumped to distributed techniques can improve oscillator performance at frequencies where LC tanks become problematic, the next figure compares, for a simulated BJT Colpitts oscillator operating at 2.3 GHz, the difference in phase-noise performance obtainable with a resonator consisting of an ideal 2-nH inductor and a  $1/4-\lambda$  transmission-line ( $11\Omega$ ,  $90^{\circ}$  long at 2.6 GHz, attenuation 0.1 dB/meter) with the transistor biased by constant-current and constant-voltage sources.

Figure 30: Shows the phase-noise performance of a 2.3-GHz BJT oscillator with a resonator consisting of an inductor (2nH) and a  $1/4-\lambda$  transmission line ( $11\Omega$ , approximating the behavior of a dielectric resonator) with bias from a constant-current source and a low-impedance, resistive constant-voltage source [1]

From the condition

$$\omega L = 1/\omega C$$

The Johnson resonant formula can be derived from this

$$f = 1/2\pi\sqrt{LC}$$

For the transmission line a hyperbolic *tanh* function is added.

Here the length of the resonator and the material Epsilon constant play a role.

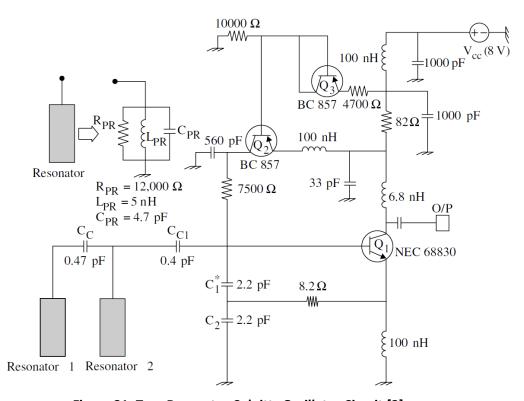

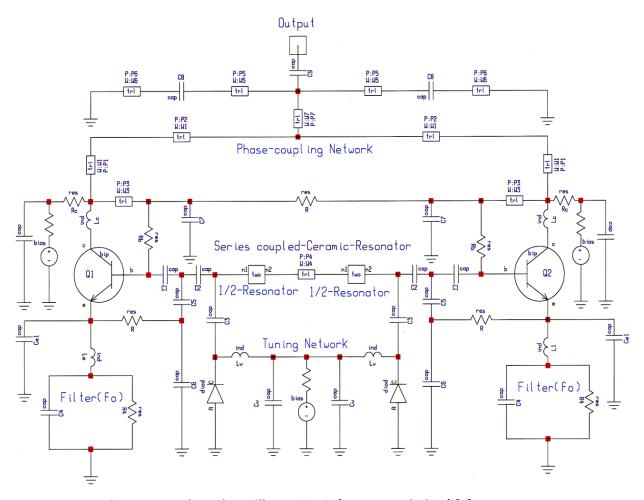

Figure 31: Two-Resonator Colpitts Oscillator Circuit [3]

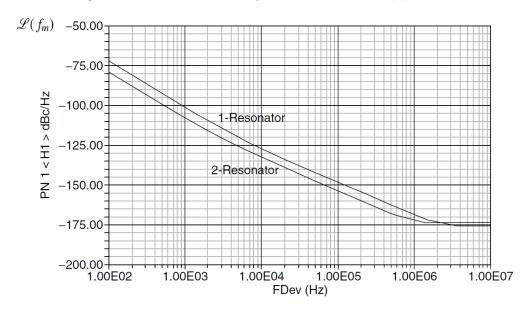

Figure 32: Simulated phase noise plot for the single resonator (1-resonator) and the coupled resonator (2-resonator) – The Phase Noise improves ~10dB with the use of a second resonator [3]

The tuning voltage (port) is typically connected to a PLL loop. Some versions use a coarse steering DC input and a modulation voltage input. For FM modulation of an auxiliary oscillator the PLL loop

bandwidth has to be less than the lowest modulation frequency. This older approach is now obsolete bus referred here for reason of completeness.

There is a practical limit how high in frequency an LC or equivalent oscillator should be design.

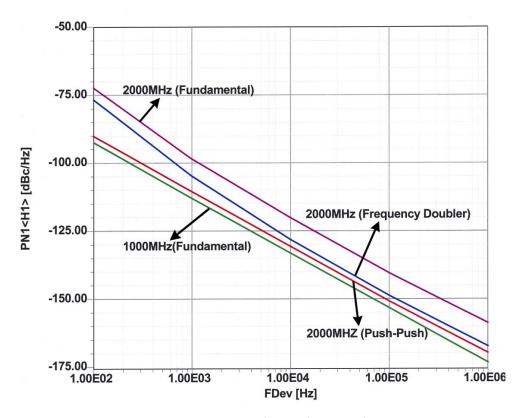

As the mechanical parts get lossy and the tuning diodes approach their cut off frequency, it is better to stay at a lower frequency, and double the frequency. The push-push oscillator solves this very well.

In the push-push circuit the fundamental frequency is ideally canceled and the first harmonic is available with better phase noise that a design at this frequency. See the circuit below:

Figure 33: Push-Push Oscillator Circuit (see patent below) [4]

Figure 34: Patent for Push-push oscillator [4]

Figure 35: Demonstration of the Influence of the Tuning diode

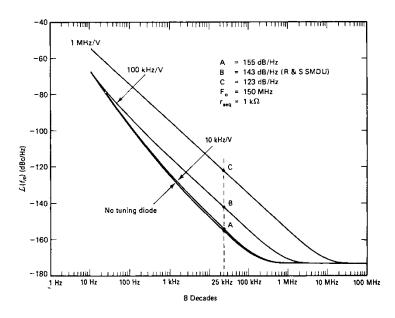

#### The influence of the tuning diode [7]:

In order to calculate the contribution of the tuning diode, it is necessary to define an equivalent noise  $R_{aeq}$  that, inserted in Nyquist's equation,

$$V_n = \sqrt{4kT_oR\Delta f} \tag{18}$$

Where,  $kT_o$  =  $4.2\times10^{-21}$  at about 300K, R is the equivalent noise resistor, and  $\Delta f$  is the bandwidth, determines an open-circuit noise voltage across the tuning diode. Practical values of  $R_{\rm deq}$  for carefully selected tuning diodes are in the vicinity of 200  $\Omega$  to 50 k $\Omega$ . If we now determine the noise voltage  $V_n = \sqrt{4\times4.2\times10^{-21}\times10,000}$ , the resulting voltage value is  $1.296\times10^{-8}\,\mathrm{V}\,\sqrt{\mathrm{Hz}}$ .

This noise voltage generated from the tuning diode is now multiplied with the VCO gain  $K_o$ , resulting in the RMS frequency deviation

$$\left(\Delta f_{\text{ms}}\right) = K_o \times \left(1.296 \times 10^{-8} \text{ V}\right) \text{ in 1 - Hz bandwidth}$$

(19)

To translate this into an equivalent peak phase deviation,

$$\theta_d = \frac{K_o \sqrt{2}}{f_m} \left( 1.296 \times 10^{-8} \right) \text{ rad in } 1 - \text{Hz bandwidth}$$

(20)

Or, for a typical oscillator gain of 100 kHz/V,

$$\theta_d = \frac{0.00183}{f_m} \text{ rad in 1 - Hz bandwidth}$$

(21)

For  $f_m$  = 2.4 kHz (typical spacing for adjacent-channel measurements for good SSB RF radios), then  $\theta_c$  =  $732 \times 10^{-9}$ . This can be converted now into the SSB signal-to-noise ratio:

$$\mathcal{L}(f_m) = 20log_{10}\frac{\theta_c}{2} = -128dBc/Hz \tag{22}$$

The tuning diode adds significant noise, so if the above mentioned 1 KHz bandwidth for the PLL is used, at 2.4 KHz the oscillator dominates.

Figure 36: Shows the influence of the diode noise of a VCO at 150 MHz [7]

In case of B and C the tuning diode greatly ruins the overall phase noise regardless of a high loaded Q! The flicker frequency component also has a huge influence on the phase noise.

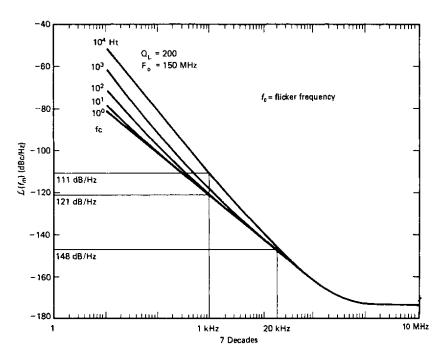

Figure 37 - shows the noise contribution of the flicker noise in a circuit with fixed Q.

Figure 37: Shows the phase noise contribution of the flicker noise to the oscillator noise [7]

At 1 KHz offset the phase noise deteriates by 10 dB.

As mentioned earlier, these voltage controlled oscillators will become part of a PLL synthesizer.

#### A modern phase noise set of equtions for an oscillator:

Calculating the phase noise from circuit parameters and using large singal parameters or derive these with the help from Besselfuntions, specifically obtaining Y21 large signal.

The total effect of all the four noise sources can be expressed as [3]

$$\pounds\left(\omega\right) = 10 \log \frac{4KT}{\omega L \times Q} \left\{ \frac{1}{2} \left[ \frac{1}{2\omega_{0}C_{eff}} \right] \left[ \frac{\omega_{0}}{\omega} \right] \right\}_{\text{Re sonator}}^{2} + 4KTr_{b} \left\{ \frac{1}{2} \left[ \frac{C_{1} + C_{2}}{C_{2}} \right] \left[ \frac{1}{2Q} \right] \left[ \frac{\omega_{0}}{\omega} \right] \right\}_{\text{base-resistan ce}}^{2} + \left[ 2qI_{b} + \frac{2\pi K_{f}I_{b}^{AF}}{\omega} \right] \left\{ \frac{1}{2} \left[ \frac{C_{2}}{C_{1} + C_{2}} \right] \left[ \frac{1}{2Q\omega_{0}C_{eff}} \right] \left[ \frac{\omega_{0}}{\omega} \right] \right\}_{\text{flic ker-base-current}}^{2} + 2qI_{c} \left\{ \frac{1}{2} \left[ \frac{C_{1}}{C_{1} + C_{2}} \right] \left[ \frac{1}{2\omega_{0}QC_{eff}} \right] \left[ \frac{\omega_{0}}{\omega} \right] \right\}_{\text{collector-current}}^{2} \right\}$$

$$(23)$$

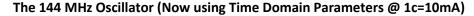

## A 144 MHz Oscillator Example: [8]

(Using Time Domain Parameters @ 1c=10mA

From the resonator  $R_P = 7056$  Ohm ( $\omega L \times Q$ )

Q of the resonator = 200 (Q of the inductor at 144 MHz)

Resonator inductance = 39nH

Resonator capacitance = 22 pF

Collector current of the transistor  $I_c = 10 \text{ mA}$

Base current of the transistor  $I_b = 85uA$ .

Flicker noise exponent AF = 2

Flicker noise constant K<sub>f</sub> = 1E-12

Feedback factor n = 5.

Phase noise @ 10 KHz:

$$PN_{(ibn+ifn)_i}(\omega_0 + 10KHz) \approx -134.2dBc / Hz$$

$$PN_{Vbn}(\omega_0 + 10KHz) \approx -151dBc / Hz$$

$$PN_{nr}(\omega_0 + 10KHz) \approx -169.6dBc / Hz$$

$$PN_{icn}(\omega_0 + 10KHz) \approx -150.6dBc / Hz$$

$$P_{out} = 5dBm$$

Figure 38: Meassured phase noise (Aeroflex) of the 144 MHz Oscillator design based on state of the art linear design, and based on optimised design using large signal parameters [8]

The value for KF=1e-12 is vaild for small currents, and in the equation above the main phase noise (measured) contribution is the resonator loss. For higher frequencies and higher output power (higher DC current, the flicker and DC current contribuion to the flicker noise will dominate. At 30 mA and higher a typical KF factor of 1e-7 is common.

Going back to the large signal phase noise analysis , the following equation is realy the most modern result [3]:

$$\pounds(\omega) = 10 \times \log \left[ k_0 + \left( \frac{k^3 k_1 \left[ \frac{Y_{21}^+}{Y_{11}^+} \right]^2 [y]^{2p}}{\left[ Y_{21}^+ \right]^3 [y]^{3q}} \right) \left( \frac{1}{(y^2 + k)} \right) \right] \left[ \frac{[1 + y]^2}{y^2} \right]$$

(24)

where

$$k_0 = \frac{kTR}{\omega^2 \,\omega_0^2 L^2 C_2^2 V_{cc}^2}$$

$$k_{1} = \frac{qI_{c}g_{m}^{2} + \frac{K_{f}I_{b}^{AF}}{4\omega}g_{m}^{2}}{\omega^{2}\omega_{0}^{4}L^{2}V_{cc}^{2}}$$

$$k_2 = \omega_0^4 (\beta^+)^2$$

$$k_3 = \omega_0^2 g_m^2$$

$$k = \frac{k_3}{k_2^2 C_2^2}$$

Where  $k_1$ ,  $k_2$ , and  $k_3$ , are constant only for a particular drive level, with  $y = \frac{C_1}{C_2}$ . Making  $k_2$  and  $k_3$  also dependent on y, as the drive level changes.

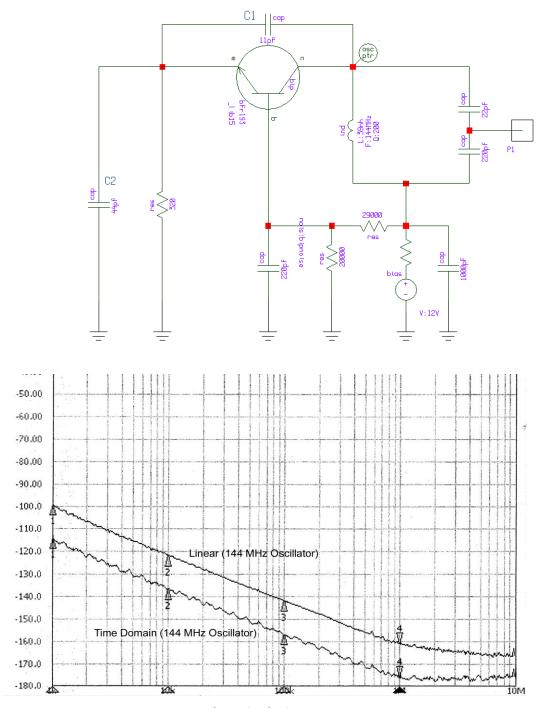

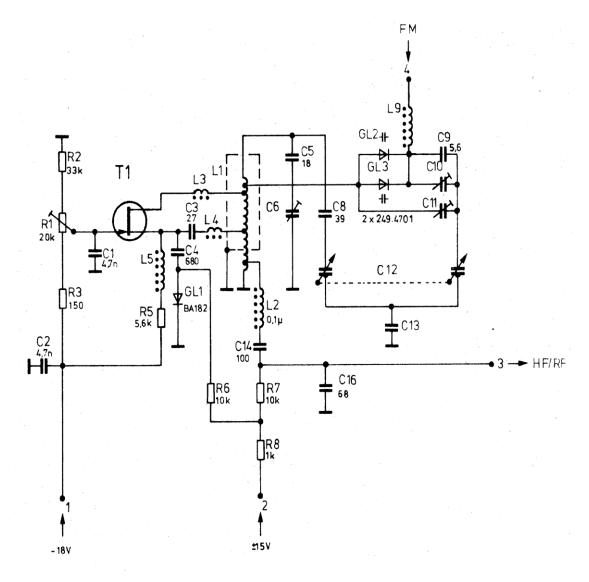

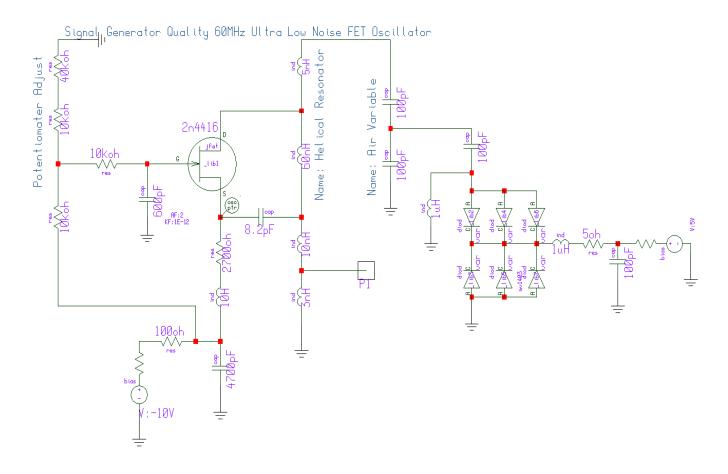

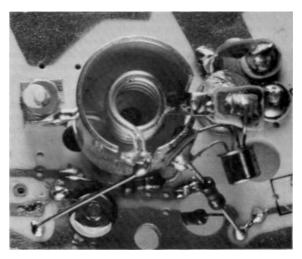

It is now of interest to look at the 1965 R&S SMDU Helix resonator based oscillator. Here is its schematic for 60MHz.

Figure 39: 60MHz Helix Resonator based Oscillator [R&S SMDU Service Manual]

It uses the 2N4416 FET and +/- 15 V source switches the oscillator on/off.

L1 is the helical resonator and C12 is the air variable capacitor.

L3, L4 and L5 are small RF chokes to avoid parasitic oscillations.

The noise improvement comes from the constant current source (5.6k $\Omega$ ) in the source; the higher voltage drop is compensated by the positive voltage at the gate.

Figure 40: Circuit diagram of the low noise VCO using a 2N4416 FET

It uses a helical resonator, as shown in figure 41. The original cicuit was modified and is using 6 aditional diodes for a wider tuning range , and the parallel combination of the diodes because of no noise cotrrelation result overall in a lower noise contribution

Figure 41: Shows the mechanical implementation of the oscilltor of fig. 40 using a helical resonator [7]

Now the phase noise will be interesting. In practice such an oscillator will have a buffer stage and it was explained above, that the buffer stage will make the far off noise worse so the result will be limited to about -165 dBc/Hz. This oscillator has an output level of 10 dBm (10mW). The theorethical noise limit is 177dB + 10 dB = 187 dBc/Hz. The differenc is due to the large signal noise figure the transistor has.

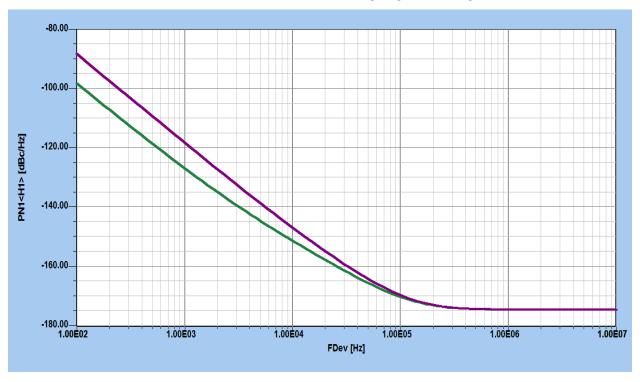

Figure 42: Shows the phase noise simulation of the 60 MHz oscillator using the helical resonator (green trace) and tuning diodes (purple trace).

The diodes makes the VCO noisier below 100KHz, but as the loop bandwidth typically (hopefully) is wider, this compensates the noise. If we look at eqn.8, we will find that the major noise contribution is the loaded Q of the resonator.

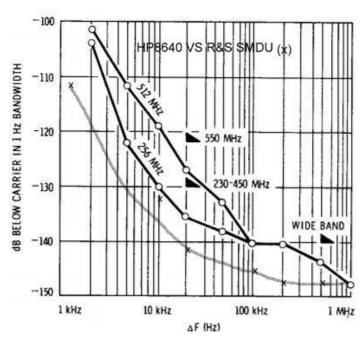

Figure 43: Comparing the phase noise of the HP8640 generator (using a mechanically tuned quarter wave resonator) and the R&S SMDU (helical resonator) tuned with an air variable capacitor

Plot shows superior performance due to the helical resonator in comparison to the mechanically tuned quarter wave resonator, as it can be tapped to achieve better impedance matching.

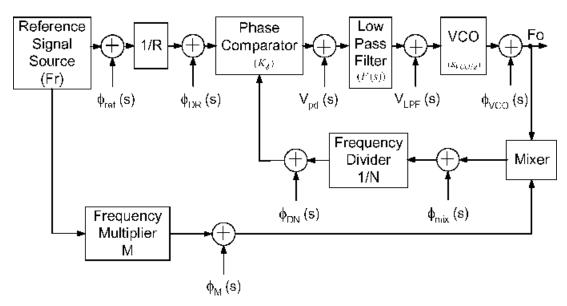

#### Principle of a PLL frequency synthesizers [1]

A PLL based frequency synthesizer, see below, is a control system that stabilizes a VCO against a frequency reference, in this case a crystal oscillator. For a good understanding here is an example. The 2 m radio aamateur frequencies are 144MHz to 148MHz (USA). Let us assume a chanell spacing of 12.5 kHz. In this case the input fom a 10 MHz frequency standard will be divided to 12.5 kHz, this is done by the reference divider R, R=800.

For a center frequency of 146MHz the N divider is set to 1168. The phase frequency detector compares the inupt from the reference divider with the main divider and changes the DC VCO frequency control volatige for the system to be in lock . The loop filter supresses the 12.5 kHz ref. frequency (to a high degree )

This is also the muliplier by which the phase/frequecy detector noise and the refence noise gets multiplied up. Let us assume for a moment that the R divider is the main noise contributor with a noise floor of -150 dBc/Hz. PN=20xlog(N), N=1168. Therefore the noisefloor insider the 146 MHz loop will be 150-81=69, reduced - 69dB/Hz.

Now to improve this we multiply the ref 10 MHz times 10 to 100Mhz, and in a mixer converter the VCO frequency to 46 Mhz and get much less division, namely N=368. In dB this is 71 dB. The in band phase noise now is 10-71 or 79dB/Hz, a 10dB improvent. This is a very simple example in preparation to explain the fractional syntesizer next. As seen from the block diagram each stage adds noise to the system.

Figure 44: PLL Based Frequency Synthesizer [1]

PLL frequency synthesizers are particularly flexible to use and to be controlled by digital commands. In addition to this they offer many distinct advantages over other forms of local oscillator for many applications both in radio communications equipment as well as test equipment, etc. As a result PLL frequency synthesizers are widely used for many RF applications. Even though other forms of generator including Direct Digital Synthesizers are available, the PLL based synthesizer has many advantages, and can often be used in conjunction with other generators including DDS circuits. The DDS circuits will be described soon. The fractional N synthesizer principle is next.

#### The Fractional-N Principle [1]

The principle of the fractional-*N* PLL synthesizer has been around for a while. In the past, implementation of this has been done in an analog system. It would be ideal to be able to build a single-loop synthesizer with a 1.25-MHz or 50-MHz reference and yet obtain the desired step size resolution, such as 25 kHz. This would lead to the much smaller division ratio and much better phase noise performance.

An alternative would be for *N* to take on fractional values. The output frequency could then be changed in fractional increments of the reference frequency. Although a digital divider cannot provide a fractional division ratio, ways can be found to accomplish the same task effectively.

The most frequently used method is to divide the output frequency by (N + 1) every M cycles and to divide by N the rest of the time. The effective division ratio is then N + 1/M, and the average output frequency is given by

$$f_o = \left(N + \frac{1}{M}\right) f_r \tag{25}$$

This expression shows that  $f_0$  can be varied in fractional increments of the reference frequency by varying M. The technique is equivalent to constructing a fractional divider, but the fractional part of the division is actually implemented using a phase accumulator. The phase accumulator approach is

illustrated by the following example. This method can be expanded to frequencies much higher than 6 GHz using the appropriate synchronous dividers.

**Example:** Considering the problem of generating 899.8 MHz using a fractional-*N* loop with a 50-MHz reference frequency,

899.8 MHz = 50 MHz

$$\left(N + \frac{K}{F}\right)$$

following equation:

The integral part of the division N has to be set to 17 and the fractional part  $\frac{K}{F}$  needs to be  $\frac{996}{1000}$ ; (the

fractional part  $\frac{K}{F}$  is not an integer) and the VCO output has to be divided by 996  $\times$  every 1000 cycles.

This can easily be implemented by adding the number 0.996 to the contents of an accumulator every cycle. Every time the accumulator overflows, the divider divides by 18 rather than by 17. Only the fractional value of the addition is retained in the phase accumulator. If we move to the lower band or try

to generate 850.2 MHz, N remains 17 and  $\frac{K}{F}$  becomes  $\frac{4}{1000}$  . This method of using fractional division

was first introduced by using analog implementation and noise cancellation, but today it is implemented totally as a digital approach. The necessary resolution is obtained from the dual modulus prescaling, which allows for a well-established method for achieving a high-performance frequency synthesizer operating at UHF and higher frequencies. Dual-modulus prescaling avoids the loss of resolution in a system compared to a simple prescaler; it allows a VCO step equal to the value of the reference frequency to be obtained. This method needs an additional counter and the dual modulus prescaler then divides one or two values depending upon the state of its control. The only drawback of prescalers is the minimum division ratio of the prescaler for approximately  $N^2$ . The dual modulus divider is the key to implementing the fractional-N synthesizer principle. Although the fractional-N technique appears to have a good potential of solving the resolution limitation, it is not free of having its own complications. Typically, an overflow from the phase accumulator, which is the adder with the output feedback to the input after being latched, is used to change the instantaneous division ratio. Each overflow produces a jitter at the output frequency, caused by the fractional division, and is limited to the fractional portion of the desired division ratio.

In our case, we had chosen a step size of 200 kHz, and yet the discrete sidebands vary from 200kHz for  $\frac{K}{F} = \frac{4}{1000}$  to 49.8MHz for  $\frac{K}{F} = \frac{996}{1000}$ . It will become the task of the loop filter to remove those discrete spurious. While in the past the removal of the discrete spurs has been accomplished by using analog techniques, various digital methods are now available. The microprocessor has to solve the

$$N^* = \left(N + \frac{K}{F}\right) = \left[N(F - K) + (N + 1)K\right]$$

(26)

#### Example – To generate 850.2MHz with a 50MHz reference:

For  $F_O$  = 850.2 MHz, we obtain:

$$N* = \frac{850.2 \text{ MHz}}{50 \text{ MHz}} = 17.004$$

Following the formula above:

$$N^* = \left(N + \frac{K}{F}\right) = \frac{\left[17(1000 - 4) + (17 + 1) \times 4\right]}{1000}$$

$$=\frac{[16932+72]}{1000}=17.004$$

$$F_{out} = 50 \text{ MHz} \times \frac{[16932 + 72]}{1000}$$

By increasing the number of accumulators, frequency resolution much below 1-Hz step size is possible with the same switching speed.

There is an interesting, generic problem associated with all fractional-N synthesizers. Assume for a moment that we use our 50-MHz reference and generate a 550-MHz output frequency. This means our division factor is 11. Aside from reference-frequency sidebands (± 50 MHz) and harmonics, there will be no unwanted spurious frequencies. Of course, the reference sidebands will be suppressed by the loop filter by more than 90 dB. For reasons of phase noise and switching speed, a loop bandwidth of 100 kHz has been considered. Now, taking advantage of the fractional-N principle, say we want to operate at an offset of 30 kHz (550.03 MHz). With this new output frequency, the inherent spurious-signal reduction mechanism in the fractional-N chip limits the reduction to about 55 dB. Part of the reason why the spurious-signal suppression is less in this case is that the phase-frequency detector acts as a mixer, collecting both the 50-MHz reference (and its harmonics) and 550.03 MHz. Mixing the 11th reference harmonic (550 MHz) and the output frequency (550.03 MHz) results in output at 30 kHz; since the loop bandwidth is 100 kHz, it adds nothing to the suppression of this signal. To solve this, we could consider narrowing the loop bandwidth to 10% of the offset. A 30-kHz offset would equate to a loop bandwidth of 3 kHz, at which the loop speed might still be acceptable, but for a 1-kHz offset, the necessary loop bandwidth of 100 Hz would make the loop too slow. A better way is to use a different reference frequency--one that would place the resulting spurious product considerably outside the 100-kHz loopfilter window. If, for instance, we used a 49-MHz reference, multiplication by 11 would result in 539 MHz. Mixing this with 550.03 MHz would result in spurious signals at ±11.03 MHz, a frequency so far outside the loop bandwidth that it would essentially disappear. Starting with VHF, low-phase-noise crystal oscillator, such as 130 MHz, one can implement an intelligent reference-frequency selection to avoid these discrete spurious signals. An additional method of reducing the spurious contents is

maintaining a division ratio greater than 12 in all cases. Actual tests have shown that these reference-based spurious frequencies can be repeatable suppressed by 80 to 90 dB.

#### **Spur-Suppression Techniques**

While several methods have been proposed in the literature, the method of reducing the noise by using a sigma-delta modulator has shown to be most promising. The concept is to get rid of the low-frequency phase error by rapidly switching the division ratio to eliminate the gradual phase error at the discriminatory input. By changing the division ratio rapidly between different values, the phase errors occur in both polarities, positive as well as negative, and at an accelerated rate that explains the phenomenon of high-frequency noise push-up. This noise, which is converted to a voltage by the phase/frequency discriminator and loop filter, is filtered out by the low-pass filter. The main problem associated with this noise shaping technique is that the noise power rises rapidly with frequency. Figure 45 shows noise contributions with such a sigma-delta modulator in place.

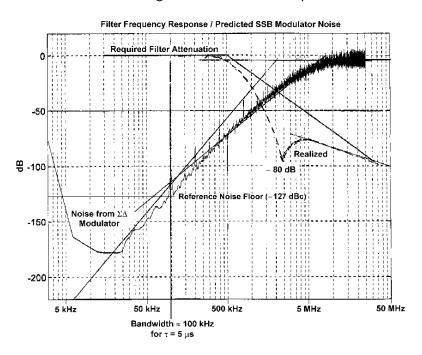

Figure 45: The filter frequency response/phase noise analysis graph shows the required attenuation for the reference frequency of 50 MHz and the noise generated by the sigma-delta converter (three steps) as a function of the offset frequency [1]

It becomes apparent that the sigma-delta converter noise dominates above 80 kHz unless attenuated.

On the other hand, we can now, for the first time, build a single-loop synthesizer with switching times as fast as 6  $\mu$ s and very little phase-noise deterioration inside the loop bandwidth, as seen in Figure 45. Since this system maintains the good phase noise of the ceramic-resonator-based oscillator, the resulting performance is significantly better than the phase noise expected from high-end signal generators. However, this method does not allow us to increase the loop bandwidth beyond the 100-kHz limit, where the noise contribution of the sigma-delta modulator takes over.

Table 1 shows some of the modern spur-suppression methods. These three-stage sigma-delta methods with larger accumulators have the most potential.

Table 1

| Technique              | Feature                     | Problem              |

|------------------------|-----------------------------|----------------------|

| DAC Phase Estimation   | Cancel Spur by DAC          | Analog Mismatch      |

| Pulse Generation       | Insert Pulses               | Interpolation Jitter |

| Phase Interpolation    | Inherent Fractional Divider | Interpolation Jitter |

| Random Jittering       | Randomize Divider           | Frequency Jitter     |

| Sigma-Delta Modulation | Modulate Division Ratio     | Quantization Noise   |

The power spectral response of the phase noise for the three-stage sigma-delta modulator is calculated from:

$$L(f) = \frac{(2\pi)^2}{12 \cdot f_{ref}} \cdot \left[ 2\sin\left(\frac{\pi - f}{f_{ref}}\right) \right]^{2(n-1)} rad^2 / Hz$$

(27)

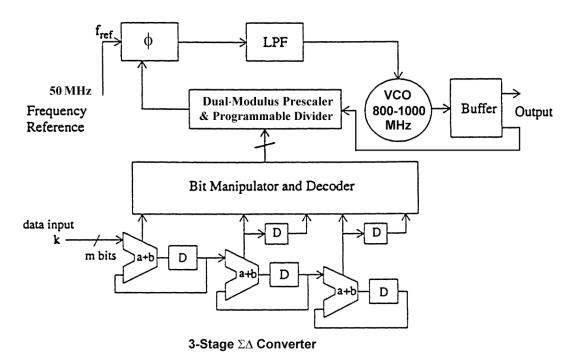

where *n* is the number of the stage of the cascaded sigma-delta modulator. Eq. (6-65) shows that the phase noise resulting from the fractional controller is attenuated to negligible levels close to the center frequency, and further from the center frequency, the phase noise is increased rapidly and must be filtered out prior to the tuning input of the VCO to prevent unacceptable degradation of spectral purity. A loop filter must be used to filter the noise in the PLL loop. Figure 45 showed the plot of the phase noise versus the offset frequency from the center frequency. A fractional-*N* synthesizer with a three-stage sigma-delta modulator as shown in Figure 46 has been built. The synthesizer consists of a phase/frequency detector, an active low-pass filter (LPF), a voltage-controlled oscillator (VCO), a dual-modulus prescaler, a three-stage sigma-delta modulator, and a buffer. Figure 47 shows the inner workings of the chip in greater detail.

After designing, building, and predicting the phase noise performance of this synthesizer, it becomes clear that the measuring of the phase noise of such a system becomes tricky. Standard measurement techniques that use a reference synthesizer would not provide enough resolution because there are no synthesized signal generators on the market sufficiently good enough to measure such low values of phase noise. Therefore, we had to build a comb generator that would take the output of the oscillator and multiply this up 10 to 20 times.

Figure 46: Fractional-N Division Synthesizer [1]

The Frac-N is found mostly in very low power applications like portable two way radios but circuits with DDS designs are taken over for high performance applications.

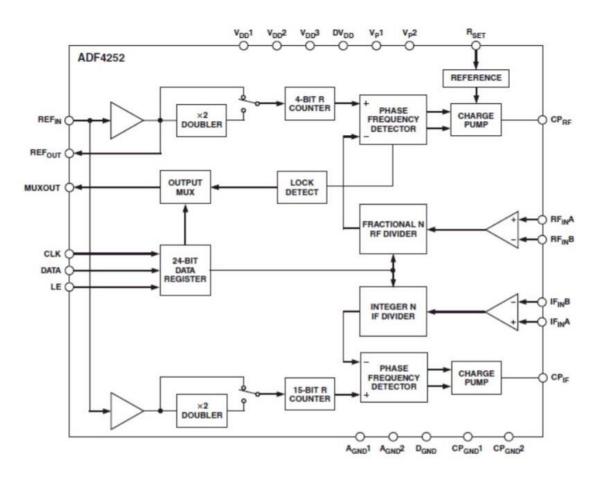

The next diagram shows the block diagram of a typical commercially available Frac-N IC from Analog Devices.

Figure 47: Typical Commercially available Frac-N IC ADF4252

#### Now, some examples for single or dual loop PLL stages for best phase noise:

The following are examples of high Q resonators locked against a simple PLL. The configuration of each case is explained. They are oscillators as used as auxiliary frequency sources in generators.

First Loop: Internal 800 MHz SAW Oscillator locked to 10 MHz, PLL IC is HMC698 Integer N

Second Loop: 13.5 GHz DRO locked to 800 MHz SAW, PLL IC is RFDIV3 IC

| Bo                 | R&S FSUP 50 Signal Source Analyzer |                      |             |         |    |        | LOCKED |

|--------------------|------------------------------------|----------------------|-------------|---------|----|--------|--------|

| \$                 | Settings                           | Residual Noise [1    | Spur List   |         |    |        |        |

| Signal Frequency:  | 13.500000 GHz                      | Int PHN (10.0 30.0 M | ) -51.5 dBc | 60.001  | Hz | -52.92 | dBc    |

| Signal Level:      | 12.31 dBm                          | Residual PM          | 0.216°      | 71.786  | Hz | -71.58 | dBc    |

| Cross Corr Mode    | Harmonic 1                         | Residual FM          | 589.989 Hz  | 119.991 | Hz | -67.70 | dBc    |

| Internal Ref Tuned | Internal Phase Det                 | RMS Jitter           | 0.0445 ps   | 179.999 | Hz | -70.18 | dBc    |

Figure 48: 13.5 GHz Dual Loop Synthesizer

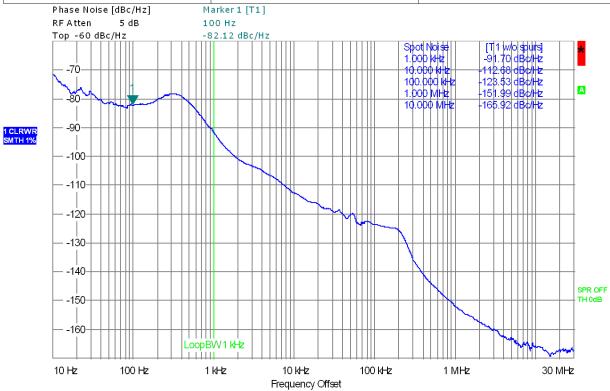

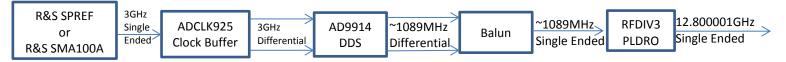

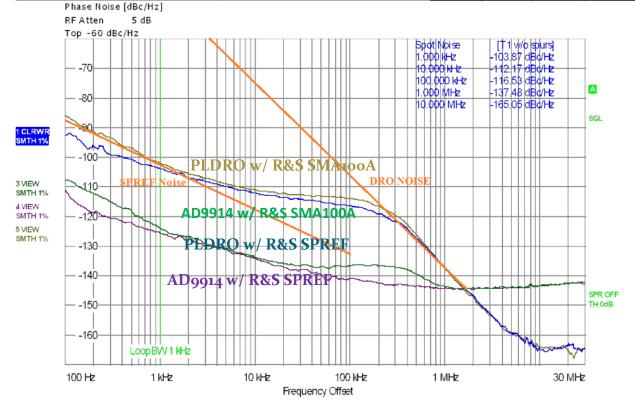

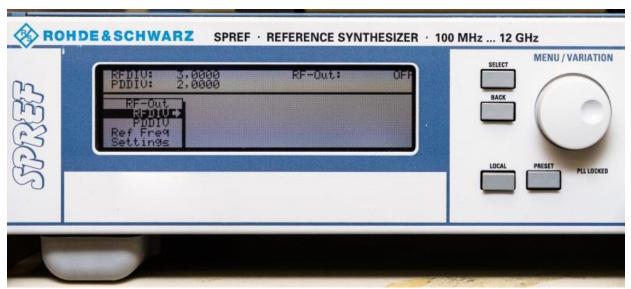

## Single Loop phase locked DRO, 1280 MHz reference

### 12.8 GHz DRO locked to 1280 MHz, PLL IC is RFDIV3

| R               | R&S FSUP 26 Signal Source Analyzer |                                         |                         |                                                                 |                                                                                    |          |

|-----------------|------------------------------------|-----------------------------------------|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|----------|

| \$              | Settings                           | Residual I                              | Noise [T1 w/o spurs]    | hase Detector +0 dB                                             |                                                                                    |          |

| Signal Frequen  | ncy: 12.799953 GHz                 | Int PHN (100.0 .                        | . 30.0 M) -65.7 dBc     |                                                                 |                                                                                    |          |

| Signal Level:   | 13.74 dBm                          | Residual PM                             | 42.013 m°               |                                                                 |                                                                                    |          |

| Cross Corr Mo   | de Harmonic 1                      | Residual FM                             | 628.208 Hz              |                                                                 |                                                                                    |          |

| Internal Ref Tu | uned Internal Phase Det            | RMS Jitter                              | 0.0091 ps               |                                                                 |                                                                                    |          |

| P ha            | se Noise [dBc/Hz] M                | arker 1 [T1]                            |                         | 1                                                               | <b>'</b>                                                                           |          |

|                 |                                    | 00 Hz                                   |                         |                                                                 |                                                                                    |          |

| Тор             | -60 dBc/Hz -9                      | 3.68 dBc/Hz                             |                         | 1.1.1.                                                          |                                                                                    | _        |

|                 | -70                                |                                         | 10                      | ot Nbise<br>1000 KHz -<br><del>.0000 KHz -</del><br>0.000 KHz - | [T1] W/b (sours)<br>-115,13 dBd/Hz<br>- <del>125,94 dBd/Hz</del><br>-124,37 dBd/Hz | <b>*</b> |

|                 | -80                                |                                         | 1.0                     | )фф MHz    -                                                    | -142.80 dBc/Hz<br>-163.37 dBc/Hz                                                   | A<br>·   |

| SMTH 1%         | 90                                 |                                         |                         |                                                                 |                                                                                    |          |

|                 | 110                                |                                         |                         |                                                                 |                                                                                    |          |

| SMTH 1%         | 130                                | *************************************** | 1                       |                                                                 |                                                                                    |          |

|                 | -140                               |                                         |                         | $\parallel \parallel \parallel \parallel \parallel$             |                                                                                    |          |

|                 |                                    |                                         |                         |                                                                 |                                                                                    | SPR OFF  |

|                 | -150                               |                                         |                         |                                                                 |                                                                                    | TH 0dB   |

|                 | LoopBW1 kHz                        |                                         |                         |                                                                 | The second second                                                                  |          |

| 100             | )Hz 1kHz                           | 10 kHz                                  | 100 kHz<br>uency Offset | 1 MHz                                                           | 30 MHz                                                                             |          |

Figure 49: Single Loop phase locked DRO, 1280 MHz reference

#### FSFLO13G00-100-1

Single Loop phase locked VCO, 100 MHz reference

100 MHz multiplied by 8, 13 GHz is locked to 800 MHz. PLL IC is RFDIV3

| R&S FSUP 26 Signal Source Analyzer |                    |                |                               |  |                     |  | LOCKED |  |

|------------------------------------|--------------------|----------------|-------------------------------|--|---------------------|--|--------|--|

| \$                                 | Settings           |                | Residual Noise [T1 w/o spurs] |  | Phase Detector +0 d |  |        |  |

| Signal Frequency:                  | 12.999943 GHz      | Int PHN (100.0 | . 30.0 M) -55.3 dBc           |  |                     |  |        |  |

| Signal Level:                      | 2.18 dBm           | Residual PM    | 0.139°                        |  |                     |  |        |  |

| Cross Corr Mode                    | Harmonic 1         | Residual FM    | 3.249 kHz                     |  |                     |  |        |  |

| Internal Ref Tuned                 | Internal Phase Det | RMS Jitter     | 0.0298 ps                     |  |                     |  |        |  |

Figure 50: Single Loop Frac-N phase locked 13GHz VCO with 100 MHz reference

#### KSFLO27R1-12-100

Single Loop phase locked VCO, 100 MHz reference

Comparison frequency is 100MHz; PLL IC is HMC703 Fractional N synthesizer. VCO output at 13.55 GHz, followed by a doubler.

| R&S FSUP 50 Signal Source Analyzer |                    |                               |           |                                         |                                         |  | LOCKED |

|------------------------------------|--------------------|-------------------------------|-----------|-----------------------------------------|-----------------------------------------|--|--------|

| Settings                           |                    | Residual Noise [T1 w/o spurs] |           | Phase Detector +0 dB                    |                                         |  |        |

| Signal Frequency:                  | 27.100000 GHz      | Int PHN (1.0 k 30.0 M)        | -41.5 dBc |                                         |                                         |  |        |

| Signal Level:                      | 6 dBm              | Residual PM                   | 0.681°    |                                         |                                         |  |        |

| Cross Corr Mode                    | Harmonic 1         | Residual FM                   | 8.264 kHz | *************************************** | *************************************** |  |        |

| Internal Ref Tuned                 | Internal Phase Det | RMS Jitter                    | 0.0698 ps |                                         |                                         |  |        |

Figure 51: Single Loop Frac-N phase locked VCO with 100 MHz reference

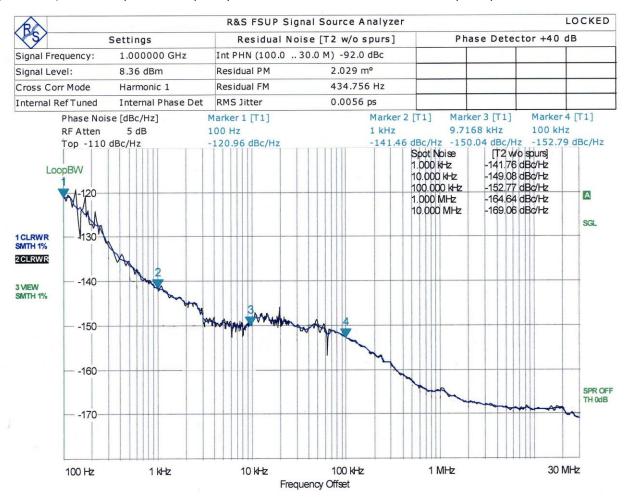

Phase locked SAW oscillator at 1 GHz.

The trick used in here is that both a mixer and a PLL IC are used to control the SAW oscillator. The PLL IC (ADF4106) is used to provide frequency lock, and the mixer is used to clean up the phase noise.

Figure 52: Phase locked SAW oscillator at 1 GHz

We have now looked at the oscillators (VCO'S) used in signal generators and at some fixed frequency oscillators. The YIG design on purpose was not yet included. To make a signal generator from an oscillator, a set of output stages are missing, including the programmable attenuator, the FM modulation capability and the AM modulation capability, placed somewhat towards the output. The FM modulations as mentioned, both analog modulation must have very low distortion.

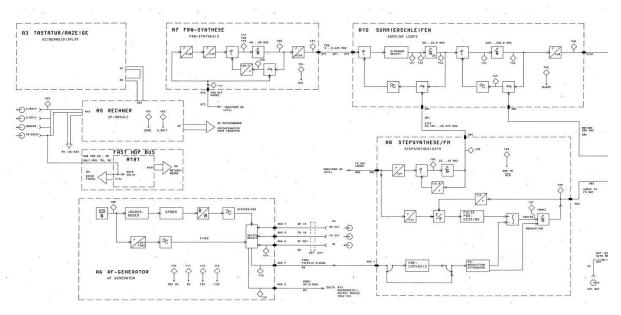

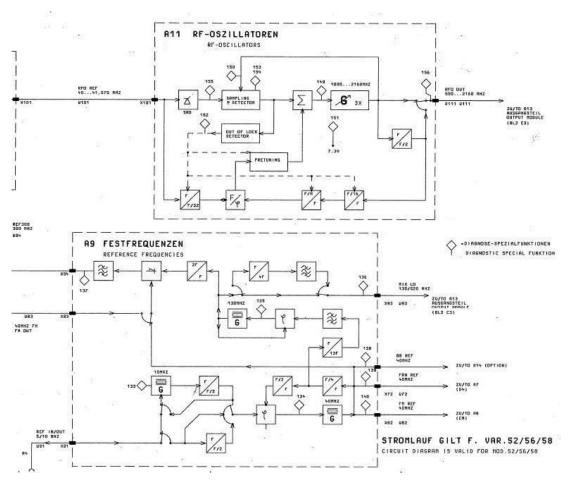

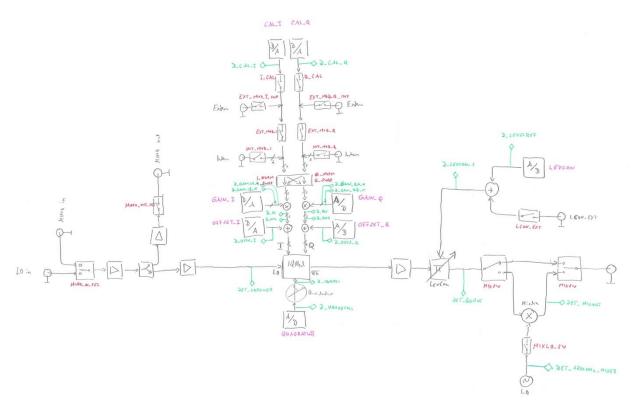

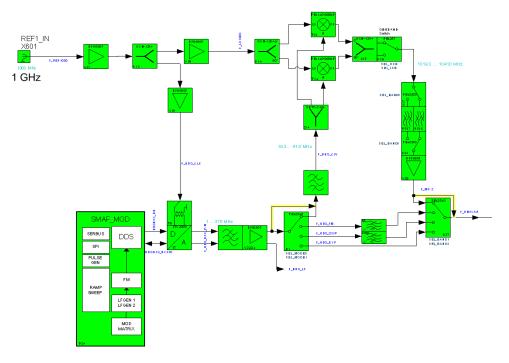

The following block diagrams are part of one of the last analog signal generators, we were now looking at the transition from the conventional designs to the more advanced circuits with DDS and wide band modulation capabilities.

Figure 53: The main systhesizer part of a "traditional" signal generator

Figure 54: Generation of reference frequency stages (variable and fixed)

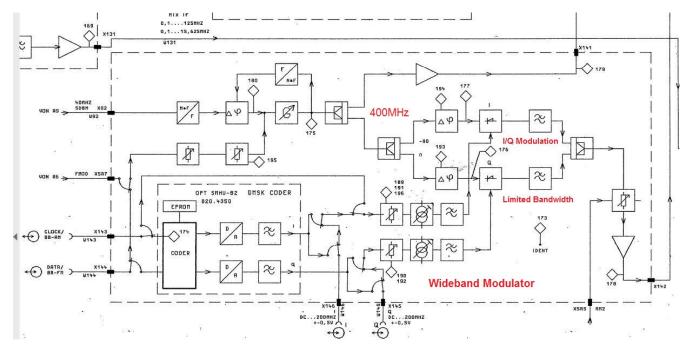

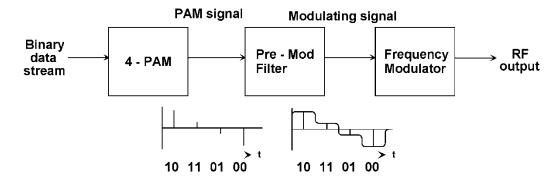

Already these "analog" signal generators used a sophisticted method for I&Q modulation, shown below (See Minimum Shift Keying option).

Figure 55: WideBand Modulators

#### **Generating Auxiliary Frequencies with Low Phase Noise**

In a conventional signal generator, a variable frequency reference is supplied to a phase-locked oscillator, which is then excited into oscillation at an adjustable frequency. A high-frequency generator may also be built around a switchable phase-locked loop. The output signal of the oscillator is supplied optionally to a frequency splitter or a series circuit of several mixers. The output of the frequency splitter is used to adjust the oscillator to a coarse frequency. In order to implement a fine adjustment, the system then switches to the output of the series-connected mixers. Unfortunately, in a signal generator of this design, it is difficult to achieve low phase noise. [5]

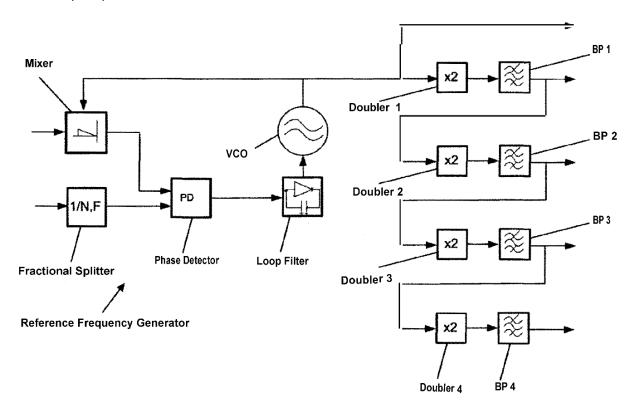

A high frequency signal generator that achieves very good secondary-line spacing with low phase noise is described in [5]. It comprises two oscillators locked by means of phase-locked loops (PLL). The first PLL generates a high-quality reference frequency, which can be tuned in small, discrete steps over approximately 10% of the operating frequency. With this restricted frequency range, a high performance voltage-controlled oscillator (VCO) can be constructed. With the use of a frequency splitter outside the PLL, the phase noise of an original fixed-frequency reference signal is largely preserved. The comparison frequency is advantageously around >10 MHz, so that rapid frequency changes are possible. Passive doubling stages with subsequent filtering are used in order to realize extremely low-noise operation. As a result of the filters between the doubling stages, undesirable harmonics are suppressed.

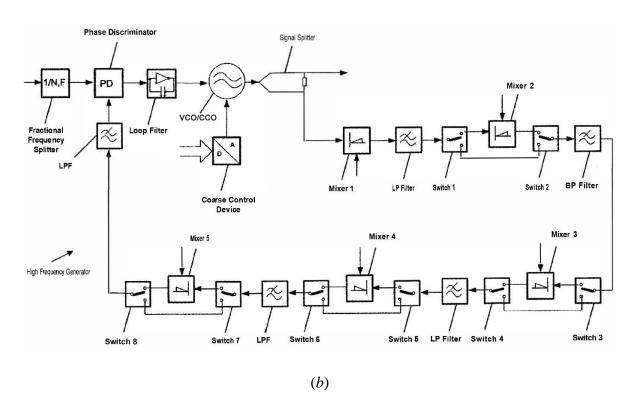

To allow the mixing-down of the VCO to the output frequency with different harmonics of the reference frequency, bridgeable mixers connected in a cascade are used. The output of the oscillators can be mixed down with the different reference signals dependent upon the position of the bridging switch. This frequency range can be further increased by using the mirror signal of the first mixer. The resulting

intermediate frequency is synchronized with a digital phase detector to a fraction of the reference frequency.

Using the reference signal as an input signal for the splitter means that the cross-products do not occur in the mixers. The mixing products are advantageously disposed on a matrix that corresponds to the last intermediate frequency divided by the resolution of the splitter. Through an appropriate choice of the splitting factors, these mixing products can be selected in such a manner that they are suppressed by the loop filter and accordingly no secondary lines occur in the synthesizer.

To allow a very rapid frequency change, the oscillator is pre-tuned based upon an individually measured characteristic of the oscillator.

#### **Detailed Description**

An example implementation of the low phase noise high frequency signal generator is shown in Figure 56(a). The system comprises a reference-frequency generator (Figure 56a) and a high-frequency generator (Figure 56b). The reference generator produces a variable reference frequency and supplies it to the high-frequency generator. The high-frequency generator PLL produces a high-frequency signal from the variable reference input. The PLL comprises at least one first mixer, a second mixer, and several switches. The first mixer, the second mixer, and the switches are connected in series. The mixers are connected into the PLL individually in a selective manner by the switches, as shown. Accordingly, an adjustable output frequency is achieved with very low phase noise. The phase noise can be further reduced by lowpass filters after each mixer.

Figure 56(a): Block Diagram of a Reference Frequency Generator [5]

Figure 56(b): Simplified block diagram of the low phase noise high frequency signal generator. (After Alexander Roth, R&S) [5]

As shown in Figure 56a, the reference generator contains a fractional frequency splitter, phase detector, loop filter, VCO, and mixer. A stable frequency reference signal of, for example, 640 MHz, is supplied to the fractional frequency splitter, which generates a signal with a frequency divided by  $N_{\text{Fref}}$  and supplies it to the phase detector. The phase detector compares this signal with a signal generated by the mixer and outputs a corresponding signal to the loop filter, which transmits it to the VCO. This generates an output signal of, for example, 650 MHz–700 MHz, and supplies it again to the mixer, where it is mixed with a stable-frequency reference signal.

In the case of a reference signal of, for example, 640 MHz, an output signal of the mixer of 10 MHz-60 MHz is obtained. The frequency of the output signal of the VCO is accordingly adjusted by setting the splitting factor  $N_{\text{Fref}}$  of the fractional splitter.

The reference-frequency generator further comprises four frequency doublers, each of which doubles the frequency of the input signal. A bandpass filter, which in each case allows only the doubled frequency to pass and filters out other components of the signals, is connected downstream of each frequency doubler. Accordingly, a reference frequency signal of 650 MHz–700 MHz in the example is present at the output of the voltage-controlled oscillator. It follows that:

- A doubled reference frequency of 1.3–1.4 GHz is present at the output of bandpass filter 1.

- A quadrupled reference frequency of 2.6–2.8 GHz is present at the output of bandpass filter 2.

- An 8-fold reference frequency of 5.2–5.6 GHz is present at the output of bandpass filter 3.

- A 16-fold reference frequency of 10.4–11.2 GHz is present at the output of bandpass filter 4.

The doubled reference frequency of 1.3–1.4 GHz is supplied to a fractional frequency splitter (Figure 56b) that divides the signal by a factor of  $N_{Fmain}$ . By multiplying the frequency of the reference signal in small steps with subsequent filtering, it is possible to achieve very low phase noise of the reference.

The output signal of the fractional frequency splitter is supplied to a phase discriminator, which compares it with the signal of the PLL and routes a corresponding output to a loop filter, and then passes it to a voltage-controlled or current-controlled oscillator (CCO), preferably an yttrium-iron-garnet (YIG) oscillator. The signal at the loop filter is used for fine adjustment of the frequency of the controlled oscillator.

A signal is supplied from a coarse-control device to the controlled oscillator for coarse adjustment of the output frequency. The output signal of the VCO is supplied to the PLL via a signal splitter. The VCO output initially passes through Mixer 1, where it is mixed with the 16-fold reference frequency. The output of the mixer is applied to a lowpass filter, which allows only the lower mixing product to pass. This signal is applied to Switch 1, which optionally applies it to Mixer 2 or bridges the mixer. If the signal is applied to Mixer 2, it is combined with the 8-fold reference frequency of 5.2–5.6 GHz in the example. Switch 2, together with Switch 1, implements the switching or the bridging function.

The resulting signal is applied to a bandpass filter, which allows only the lower product of the mixer to pass. If Mixer 2 has been bridged, the low-pass filter plays no role. The output is next applied to the combination of Switch 3 and Switch 4, which either apply the signal to Mixer 3 or bridge it. If the signal is applied to Mixer 3, it is combined with the 4-fold reference frequency of 2.6–2.8 GHz in the example. The output signal is again applied to a lowpass filter, which once again allows only the lower mixing product to pass. Here also, the filter plays no role if Mixer 3 has been bridged.

Switches 5 and 6, Mixer 4 and a lowpass filter form another corresponding functional unit. Mixer 4 combines the input signal with the doubled reference frequency of 1.3–1.4 GHz in the example.

Switches 7 and 8, Mixer 5 and a lowpass filter form yet another corresponding functional unit. Mixer 5 combines the input signal with an unchanged reference frequency of 650–700 MHz in the example. The signal resulting after the lowpass filter is applied to the phase discriminator.

The signals with which the mixers combine the signal of the phase-locked loop are taken from the reference frequency generator (Figure 56a). Mixer 1 can also be advantageously provided with switches, in which case the mixer can also be bridged. As an alternative, a larger or smaller number of mixers can be used in the PLL system. The higher the tuning range of the oscillator, the more mixers are used. [5]

#### **Determination of Splitting Factors**

The splitting factors  $N_{\text{Fref}}$  and  $N_{\text{Fmain}}$  of the fractional splitters are adjusted in order to achieve the desired output frequency of the oscillator. An output frequency of, for example, 10000 MHz to 18000 MHz is taken as a starting point. Initially, the parameter V is calculated, which corresponds to the multiple of the reference frequency  $f_{\text{ref}}$  with which the mixing-down is to be implemented. The minimal adjustable reference frequency of 650 MHz in the example and an intermediate frequency of, for example, 55 MHz (which is favorable for the main loop), are used as a basis.

$$V = INT((f_{osz} + 55 MHz) / 650 MHz)$$

(28)

Next, the reference frequency  $f_{ref}$  is calculated. For this purpose, the previously determined V is used. Because V is rounded down to whole numbers, a reference frequency somewhat higher than 650 MHz is obtained.

$$f_{ref} = (f_{osz} + 55 \,\mathrm{MHz})/V \tag{29}$$

The value of the splitter of the reference-frequency generator is next calculated. The splitting factor  $N_{Fref}$  of the reference-frequency generator is rounded in such a manner that no secondary lines occur within the loop band-width.

$$N_{Fref} = 640 \,\mathrm{MHz} / \,\mathrm{ABS} \Big[ \left( 640 - f_{ref} \right) \Big]$$

with rounding to 1/F and

F = 8 for N < 20

$F = 4 \text{ for } 20 \le N < 40$

$F = 2 \text{ for } 40 \le N < 80$

$F = 1 \text{ for } 80 \leq N$

The rounding to different 1/F values prevents the modulation from falling below 8 MHz by a decimal component and accordingly being attenuated by the phase-locked loop.

Next, the intermediate frequency  $f_{zf}$  in the PLL of the high frequency generator is calculated. Through the rounding of the splitter in generating the reference frequency  $f_{ref}$ , an intermediate frequency  $f_{zf}$ , which differs from the set value, is obtained.

$$f_{zf} = V * 640 \,\text{MHz} * \left(1 - 1/N_{Fref}\right) - F_{osz}$$

(30)

This calculated intermediate frequency  $f_{zf}$  is now rounded to an adjustable value.

$$N_{Fmain} = 2*640 \,\text{MHz} * \left(1 - 1/N_{Fref}\right) / f_{zf} \tag{31}$$

with rounding of the splitting factor to 1/F and

F = 16 for N < 10

$F = 8 \text{ for } 10 \le N < 20$

$F = 4 \text{ for } 20 \le N < 40$

$F = 2 \text{ for } 40 \le N < 80$

$F = 1 \text{ for } 80 \leq N$

The rounding to different 1/F values prevents the modulation from falling below approximately 8 MHz by the decimal component. The resulting secondary lines are accordingly suppressed by the PLL of the high-frequency generator.

Finally, the actual frequency  $f_{osz}$  of the VCO of the high-frequency generator is calculated.

$$f_{osz} = V * 640 \,\text{MHz} * \left(1 - 1/N_{Fref}\right) - \left(2 * 640 \,\text{MHz} * \left(1 - 1/N_{Fref}\right)/N_{Fmain}\right)$$

(32)

The residual error, which arises from rounding the splitting factors  $N_{Fref}$ ,  $N_{Fmain}$ , is smaller than 1 MHz and can be tolerated. With the advantageous use of a direct-digital synthesizer in the PLL of the high-frequency oscillator instead of the fractional splitter, an arbitrary frequency resolution is possible. [5]

Now we move to the important mostly digital frequency generation domain

Part II

Overview: Direct Digital Synthesizers [9-13]

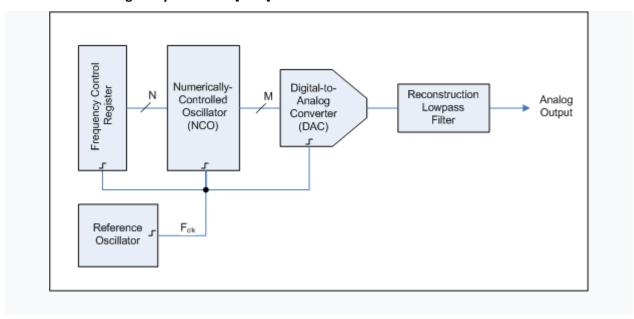

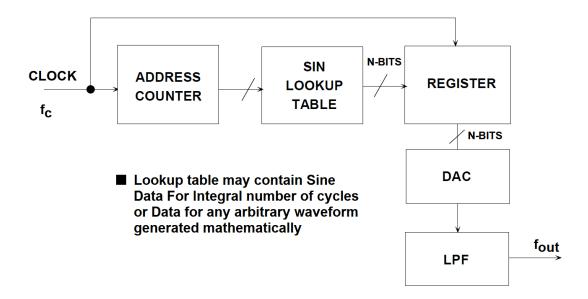

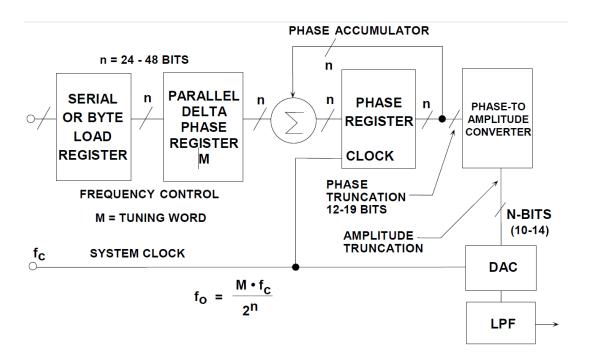

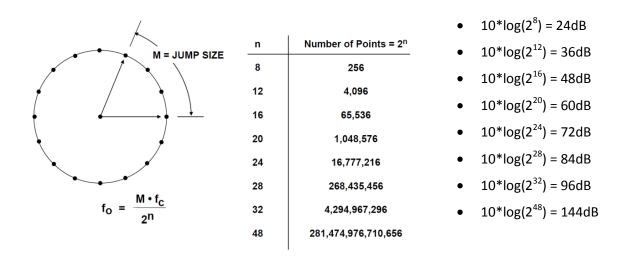

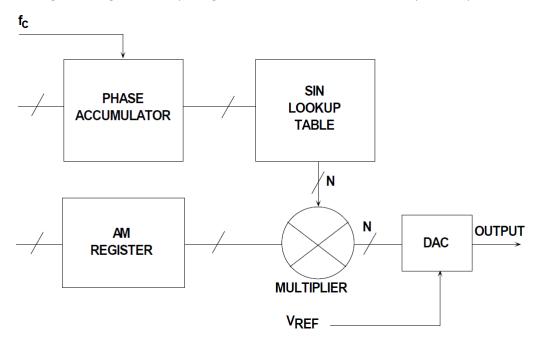

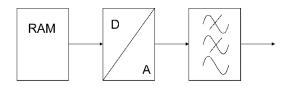

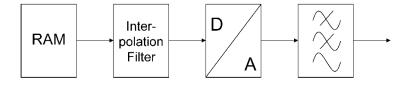

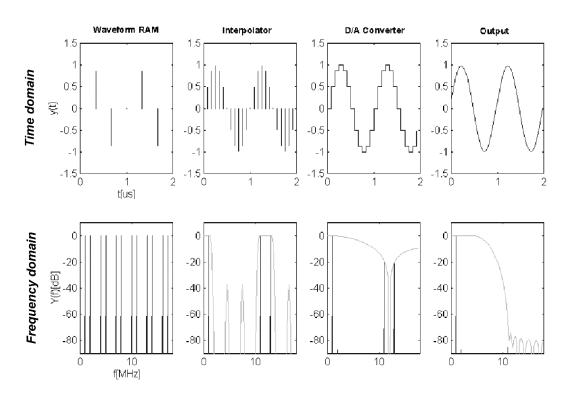

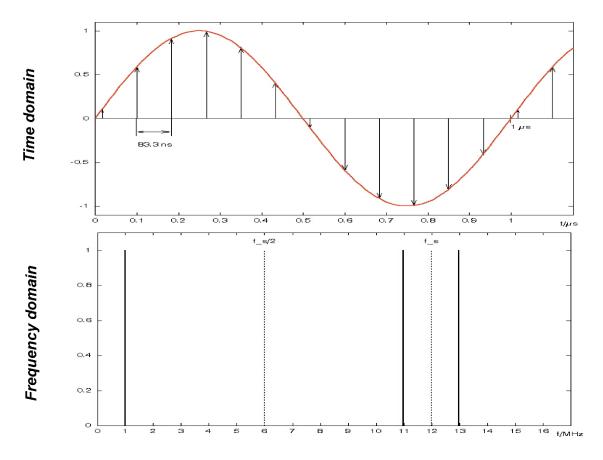

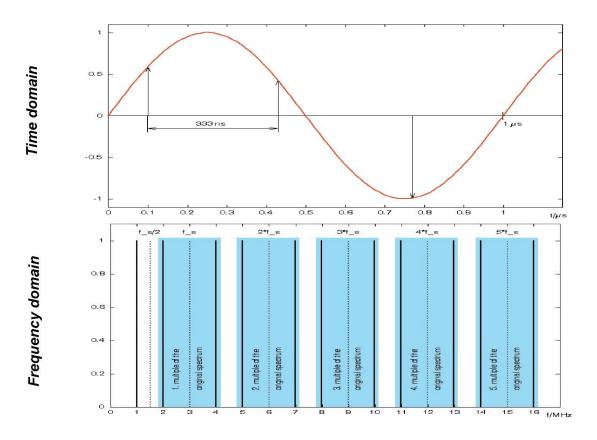

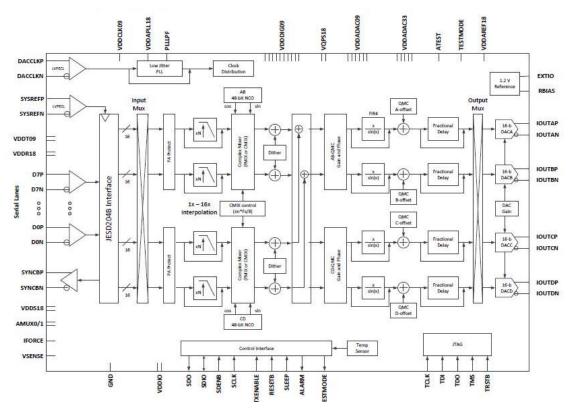

Figure 57: Direct Digital Synthesizer block diagram

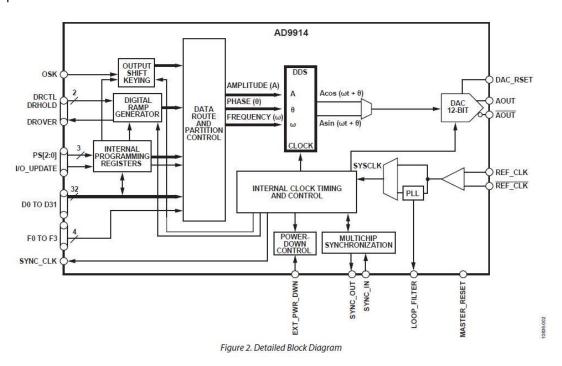

A basic Direct Digital Synthesizer consists of a frequency reference (often a crystal or SAW oscillator), a numerically controlled oscillator (NCO) and a digital-to-analog converter (DAC) as shown in Figure 57.

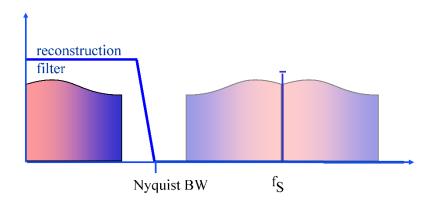

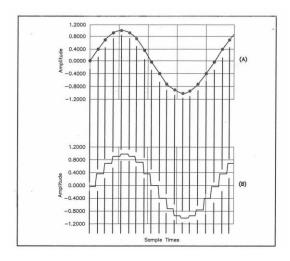

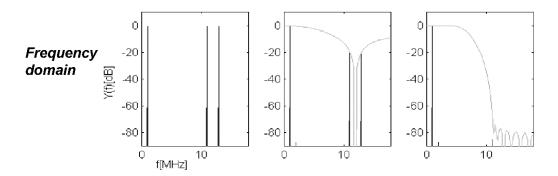

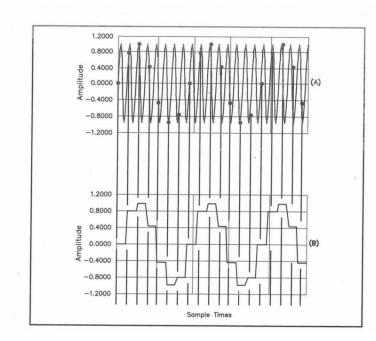

The reference oscillator provides a stable time base for the system and determines the frequency accuracy of the DDS. It provides the clock to the *NCO* which produces at its output a discrete-time, quantized version of the desired output waveform (often a sinusoid) whose period is controlled by the digital word contained in the *Frequency Control Register*. The sampled, digital waveform is converted to an analog waveform by the *DAC*. The output reconstruction filter rejects the spectral replicas produced by the zero-order hold inherent in the analog conversion process.

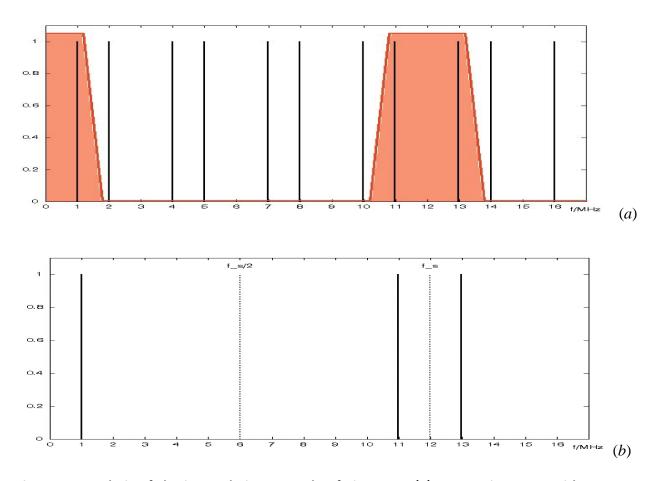

#### **Performance**

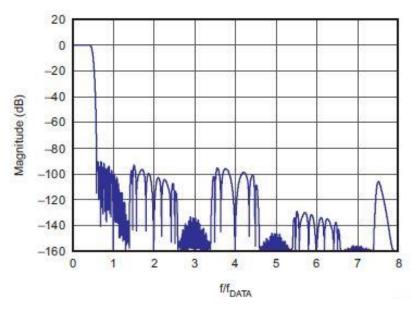

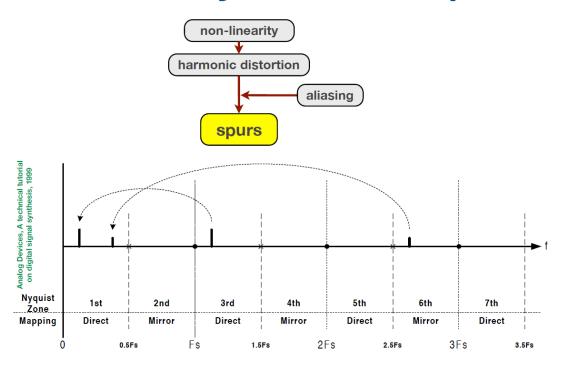

A DDS has many advantages over its analog counterpart, the phase-locked loop (PLL), including much better frequency agility, improved phase noise, and precise control of the output phase across frequency switching transitions. Disadvantages include spurs due mainly to truncation effects in the NCO, crossing spurs resulting from high order (>1) Nyquist images, and a higher noise floor at large frequency offsets due mainly to the Digital-to-analog converter.

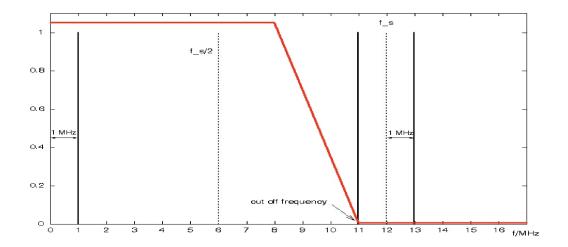

Because a DDS is a sampled system, in addition to the desired waveform at output frequency  $F_{out}$ , Nyquist images are also generated (the primary image is at  $F_{clk}$ - $F_{out}$ , where  $F_{clk}$  is the reference clock frequency). In order to reject these undesired images, a DDS is generally used in conjunction with an analog reconstruction lowpass filter as shown in Figure 57.

#### Frequency agility

The output frequency of a DDS is determined by the value stored in the frequency control register (FCR) (see Fig.57), which in turn controls the NCO's phase accumulator step size. Because the NCO operates in the discrete-time domain, it changes frequency instantaneously at the clock edge coincident with a change in the value stored in the FCR. The DDS output frequency settling time is determined mainly by the phase response of the reconstruction filter. An ideal reconstruction filter with a linear phase response (meaning the output is simply a delayed version of the input signal) would allow instantaneous frequency response at its output because a linear system cannot create frequencies that are not present at its input.

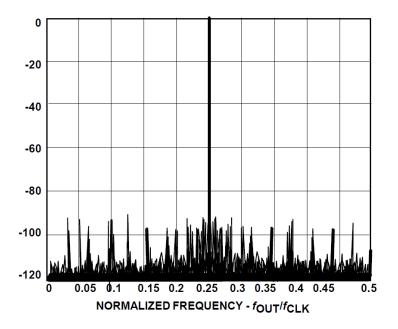

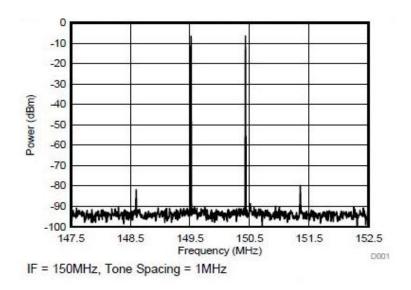

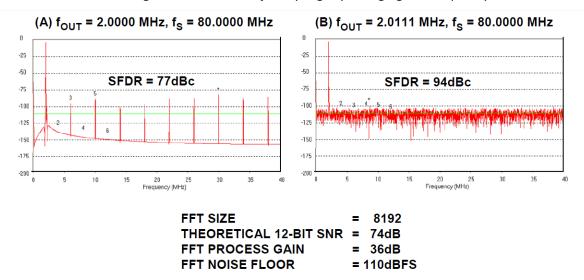

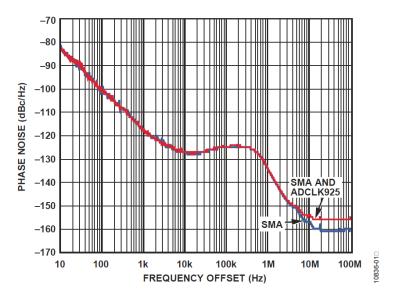

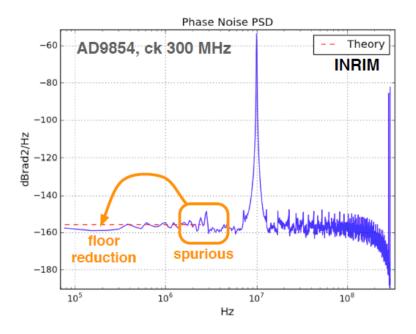

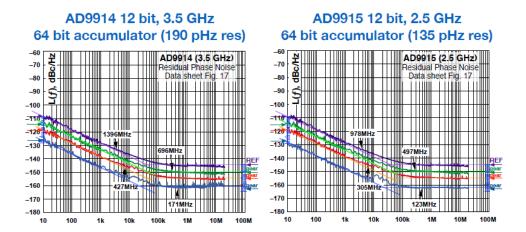

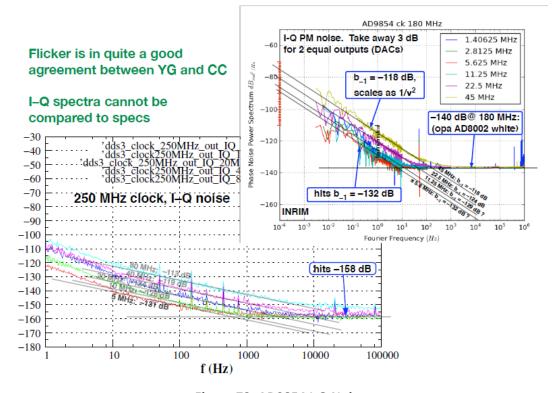

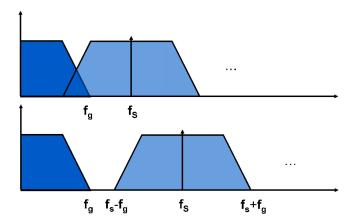

#### Phase noise and jitter